来源:机器之心

编辑:维度、陈萍

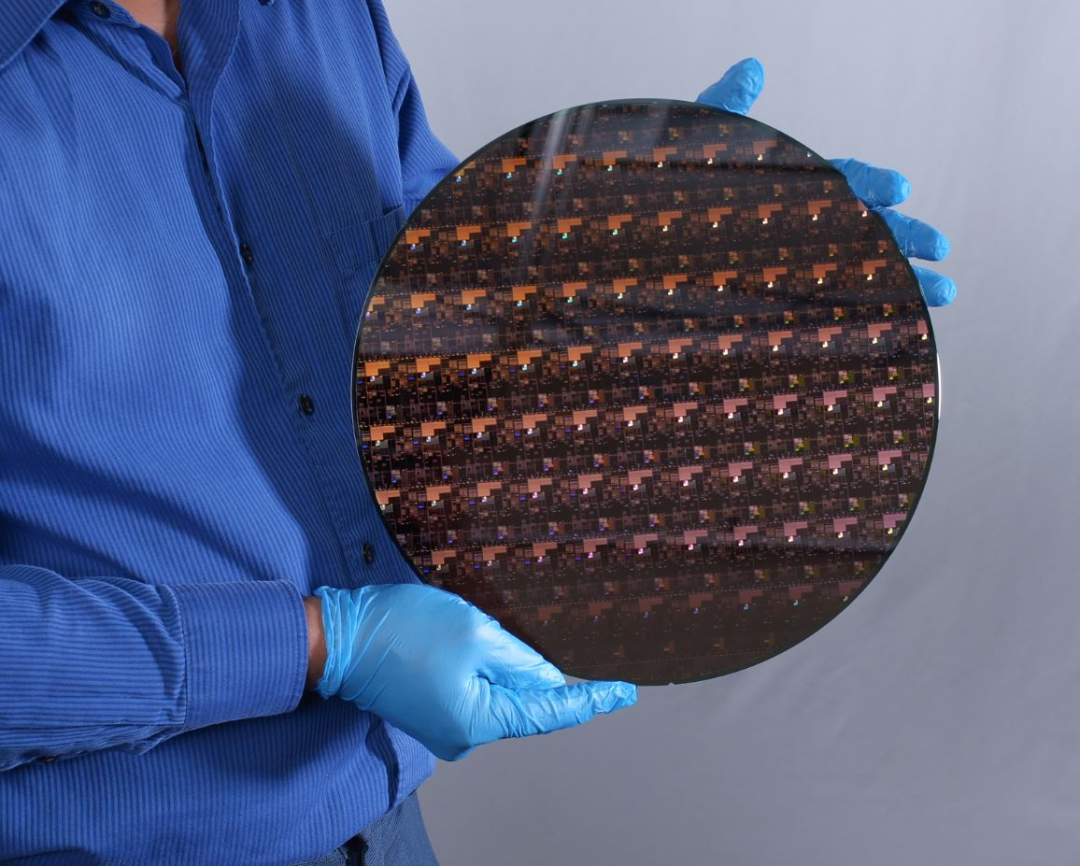

2017 年,IBM 联合三星和 GlobalFoundries 推出了首个 5nm 制程工艺的芯片。仅仅过去不到四年,IBM 又率先公布 2nm 芯片制造技术,不仅具有更高的晶体管密度,而且采用了全新的 GAA 工艺设计。与当前 7nm 和 5nm 相比,2nm 在性能和功耗上均显著提升,将为半导体行业注入新的活力。

作为计算机芯片的最基础构建块,晶体管的体积变得越来越小,相应地芯片速度变得更快且更加节能。当前,7nm 和 5nm 制程工艺是手机和笔记本电脑中所用芯片的主流选择。2021 年 3 月,三星公布了全球首款 3nm「SRAM 芯片」,并预计于 2022 年起量产。

在各大芯片厂商「你追我赶」的激励角逐中,IBM 率先秀出了全球首个 2nm 芯片制造技术。

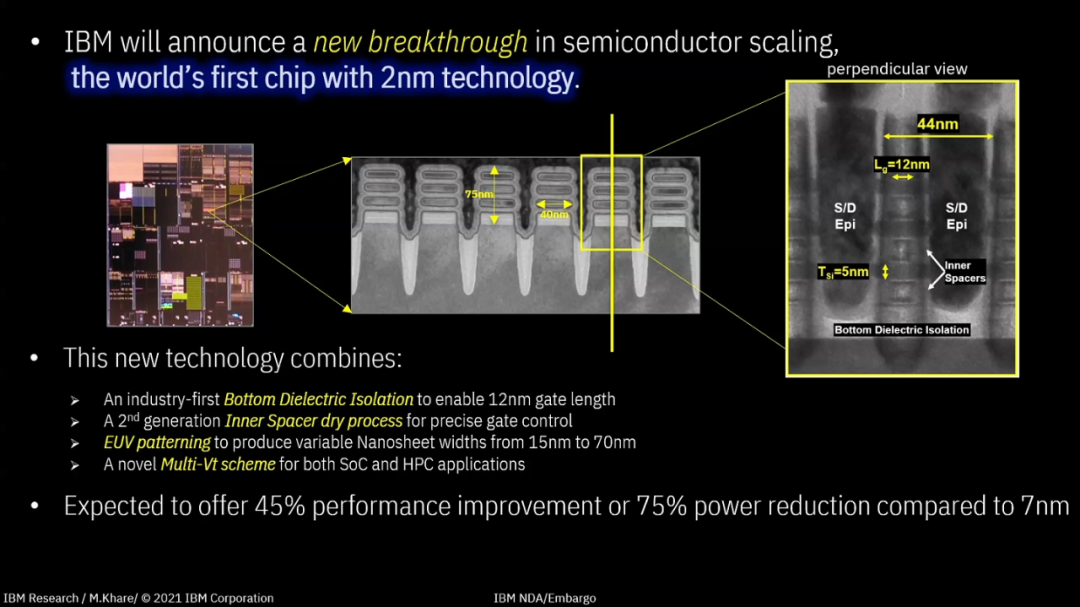

5 月 6 日晚间,IBM 公布了其在半导体设计和工艺方面的一项重要突破:全球首款采用 2nm 制程工艺的芯片,有助于将半导体行业提升到一个新的水平。与当前主流的 7nm 芯片相比,IBM 2nm 芯片的性能预计提升 45%,能耗降低 75%。与当前领先的 5nm 芯片相比,2nm 芯片的体积也更小,速度也更快。

IBM2nm制程工艺的芯片。

具体来说,2nm 芯片的潜在优势包括如下:

手机续航时长翻两番,用户充一次电可以使用四天;

大幅度减少数据中心的能源使用量;

显著提升笔记本电脑的性能,比如更快运行应用程序、完成语言翻译和互联网访问;

有助于自动驾驶汽车实现更快的目标检测和反应时间。

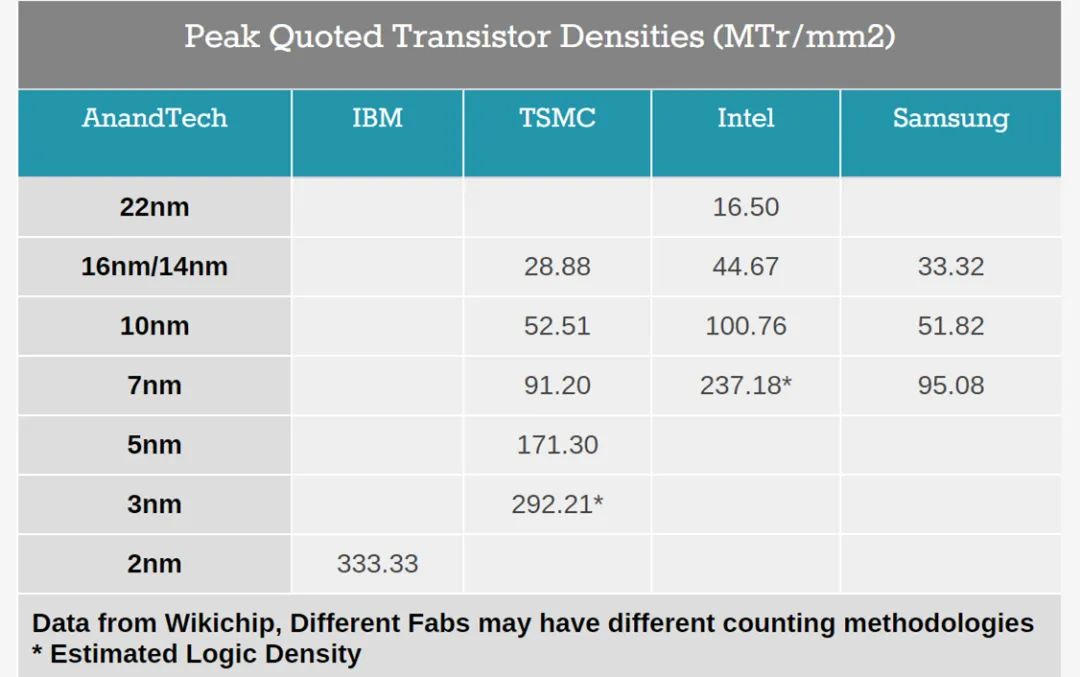

从更具体的细节来看,IBM 2nm 芯片每平方毫米容纳 3.33 亿个晶体管,对比之下,台积电 5nm 芯片每平方毫米容纳 1.713 亿个晶体管,三星 5nm 芯片每平方毫米容纳 1.27 亿个晶体管。

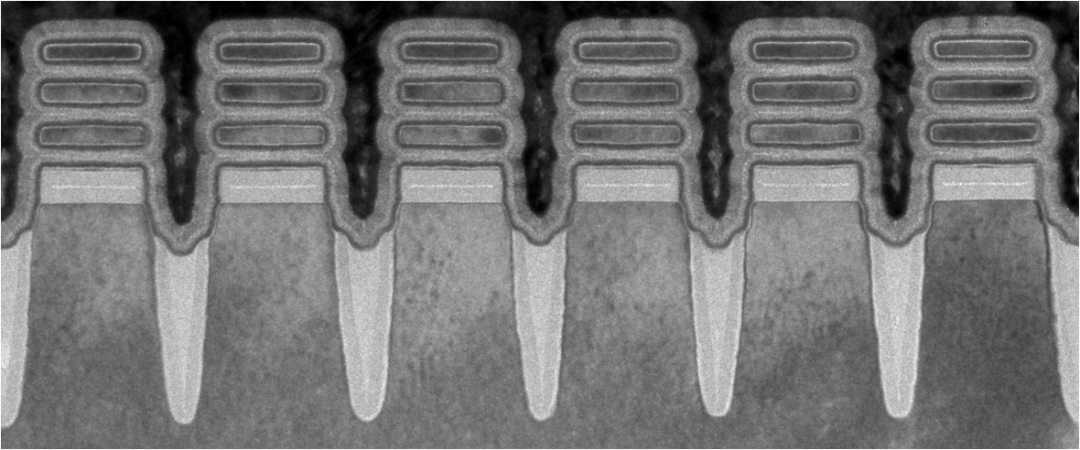

近摄镜头下的2nm晶圆。

作为曾经一家主要的芯片制造商,IBM 现在将其芯片生产外包给了三星,但依然在纽约奥尔巴尼市保留了一家芯片制造研发中心。该中心主要负责芯片的测试运行,并与三星和英特尔签署联合技术开发协议,以使用 IBM 的芯片制造技术。此次公布的 2nm 芯片正是在这里设计和制造的。

IBM 位于纽约奥尔巴尼市的芯片制造研发中心。

更高的晶体管密度、全新架构设计

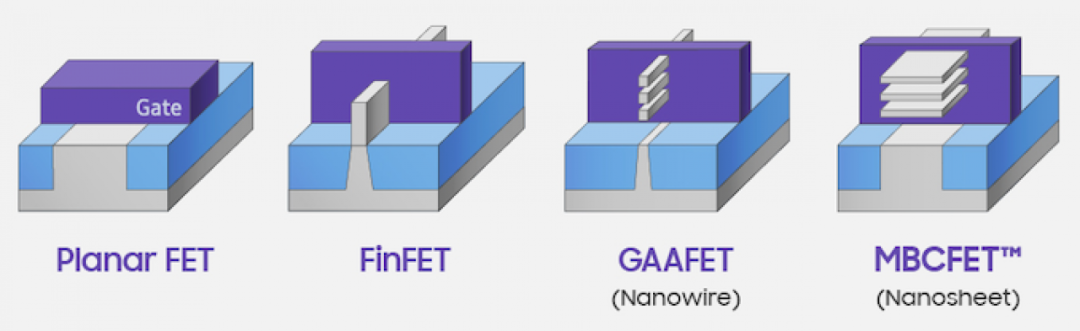

与 7 纳米处理器相比,IBM 推出的 2nm 芯片在相同功率下性能提升 45%,能效则要高出 75%。IBM 指出,他们是第一个分别在 2015 年、2017 年推出 7nm、5nm 的研究机构,后者已从 FinFET 升级为纳米片技术,从而可以更好地定制单个晶体管的电压特性。

IBM 表示,该技术可以将 500 亿个晶体管安装到一个指甲大小的芯片上,从而使处理器设计人员拥有更多选择,比如可以注入核心级创新来提高 AI 和云计算等前沿工作负载的功能,以及探寻硬件强制安全性和加密的新途径等。

如你们时常从其他报道中所了解的,不同的芯片代工厂(台积电、三星等)对晶体管密度有不同的定义。值得注意的是,这些关于密度的数字通常被列为峰值密度。

StackedGAA(切入环绕式栅极技术,gate-all-around)

关于新制程中如何制造晶体管的关键技术 Gate-All-Around / nanosheet(环绕式栅极技术晶体管),虽然 IBM 还没有明确说明,但图片显示这款新的 2nm 处理器使用了 three-stack GAA 设计。

在目前的新制程竞争中,三星计划在 3nm 节点上推出 GAA(三星将自己的技术称为 MBCFET)。其计划在 2020 年底即开始 MBCFET 的风险试产,2021 年规模量产,同时在 2021 年推出第一代 MBCFET 的优化版本。台积电则仍希望在 3nm 上继续使用 FinFET ,等到 2nm 芯片才会推出 GAA。根据规划,台积电的 2nm 工艺会在 2023 年开始风险试产,2024 年量产。

相比之下,可以预见英特尔将在其 5nm 工艺上引入某种形式的 GAA。预计到 2023 年,这家公司会在 5nm 节点上放弃 FinFET,转向 GAA 环绕栅极晶体管。

正如目前大规模应用的 FinFET 工艺拯救了芯片产业,在 5nm 以下的时代,GAAFET 或将成为半导体产业继续向前发展的关键。不过,GAAFET 工艺的制造难度显然是极高的。

IBM 的 3-stack GAA 设计采用了 75nm 的单元高度,40nm 的单元宽度,单个纳米片的高度为 5nm,彼此之间间隔 5nm。栅极间距为 44nm,栅极长度为 12nm。IBM 表示,3-stack GAA 是首个采用底部介电隔离通道的设计,这使得 12nm 栅长成为可能,并且其内部的间隔器采用第二代干式工艺设计,有助于纳米片的开发。

在实施过程中,IBM 还广泛地使用 EUV 技术,并包括在芯片过程的前端进行 EUV 图案化,而不仅是在中间和后端,后者目前已被广泛应用于 7nm 工艺。重要的是,IBM 这个芯片上的所有关键功能都将使用 EUV 光刻技术进行蚀刻,IBM 也已经弄清楚了如何使用单次曝光 EUV 来减少用于蚀刻芯片的光学掩模的数量。

目前,还没有提供关于 2nm 测试芯片的细节,现阶段,它可能是一种简化的 SRAM 测试工具,逻辑不多。IBM 表示,测试设计使用 multi-Vt 方案来进行高性能和高效率的应用演示。

虽然 2nm 制程工艺的芯片在性能和能耗方面都较当前 7nm 和 5nm 更强,但很大程度上只是概念验证,离上市还有很长一段时间。在 2015 年 7 月,同样是 IBM 率先宣布制成了 7nm 芯片,而直到 2019 年下半年,人们才能买到带有 7nm 芯片的手机。

据悉,2nm 制程的技术大概需要几年的时间才能进入市场。

参考链接:

https://www.anandtech.com/show/16656/ibm-creates-first-2nm-chip

https://www.reuters.com/technology/ibm-unveils-2-nanometer-chip-technology-faster-computing-2021-05-06/

https://www.theverge.com/2021/5/6/22422815/ibm-2nm-chip-processors-semiconductors-power-performance-technology

https://newsroom.ibm.com/2021-05-06-IBM-Unveils-Worlds-First-2-Nanometer-Chip-Technology,-Opening-a-New-Frontier-for-Semiconductors#assets_all

CVPR 2021 线下论文分享会

为更好的服务 AI 社区,促进国内计算机视觉学术交流,机器之心计划于 6 月 12 日组织大型「CVPR 2021 线下论文分享会」。

本次活动将设置Keynote、 论文分享和 Poster 环节,邀请顶级专家、论文作者与现场参会观众共同交流。欢迎论文作者、AI 社区从业者们积极报名参与。

©THEEND