TechWeb 文 /薛定谔之咸鱼

在3月9日的苹果春季发布会上苹果发布了诸多新品,其中最亮眼的当属苹果顶级旗舰芯片M1 ULTRA。那么作为M1系列最后一款芯片,M1 ULTRA到底怎么样呢?

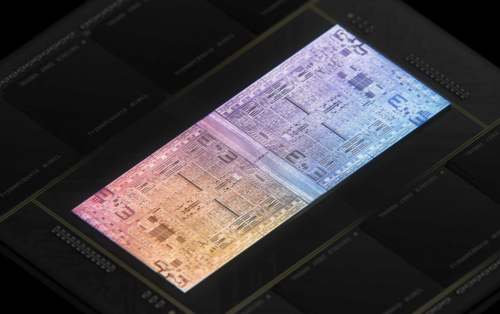

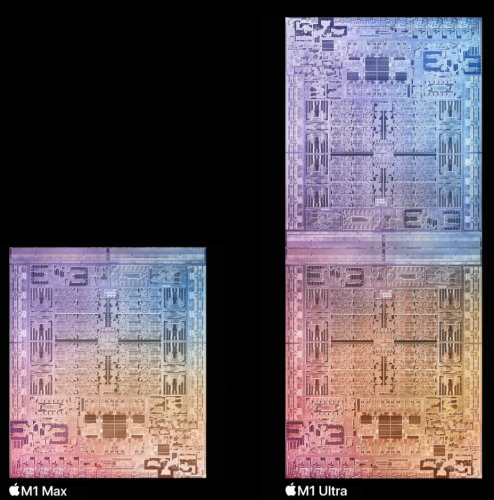

1个 M1 ULTRA =2个M1 Max

如果用一句话简单概括一下M1 ULTRA那就是:将2枚M1 Max通过封装融合成一体,成为一枚芯片。

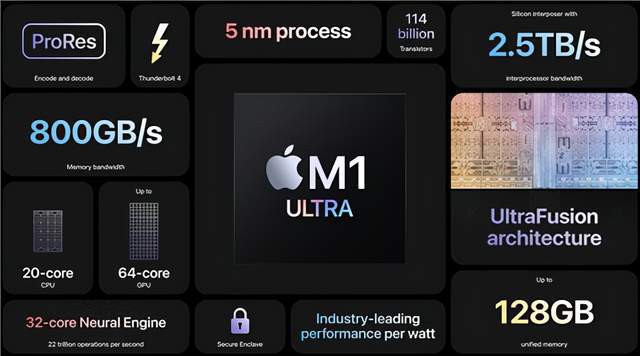

M1 Max实现了突破性的Die-to-Die(裸片到裸片)技术,因此可以基于两个M1 Max的裸片扩展为M1 ULTRA,通过创新性的定制架构UltraFusion连接在一起,带来两倍的性能表现。UltraFusion架构采用硅中介层连接一万余个信号点,在两个裸片之间实现了2.5TB/s的低延迟处理器互联带宽。

从目前公布的信息看,苹果早在开发M1 Max时就考虑到了这种“双芯融合”的方案,在芯片版图的上为将来的Die-to-Die连接预留了位置。那么这样做有什么好处呢?

性能提升

对于目前的苹果来说,目前所使用的台积电5nm工艺已经算是业界最顶尖的工艺了,台积电的3nm还在路上。那么这种情况下,苹果想推出一款性能更强的芯片该怎么办呢?这时有两种办法:

是再设计一款面积更大的芯片。

是将原来的芯片组合在一起使用,也就是说一次用两颗。

对于熟悉半导体行业的朋友来说应该都对5nm芯片高昂的造价有所耳闻,再设计一款面积更大的芯片,即使是苹果成本上也很难抗住。那么就剩下第二条了,将两个芯片或者更多数量的已有芯片合在一起使用。

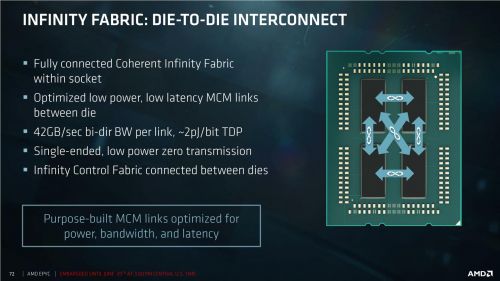

如果想把两枚芯片连在一起用,目前业界的主流做法是通过主板PCB连接。

比如像这款华硕的WS C621E SAGE 主板就属于双路CPU主板,在设计之初就支持两块CPU同时工作。

但这样做缺点也很明显,比如两个CPU的插槽以及相应连接所需的布线明显会占用很大的PCB面积,这样做出来的产品尺寸会很大。而且由于两个CPU之间是通过PCB走线连接,延迟会变得很大。

在这里我们不难发现,通过主板PCB连接两块CPU所带来的缺点基本都是连线过长导致的,那么缩短两个芯片之间的连线距离不就可以解决了吗?“胶水双核”由此出现了。

“胶水双核”是指使用特殊方法将两个或更多芯片封装在一起制造的处理器。由于这种特殊方法像是将两个或更多核心用胶水粘在一起,由此而得名“胶水双核”。

“胶水双核”技术最早可以追溯到1995年的英特尔的Pentium Pro,但这并不是一项落后的技术。

比如AMD一代EPYC(霄龙)处理器就采用了这种所谓的“胶水双核”技术。在图上可以清晰地看出,它将4颗Die(裸片)封装到了一颗CPU中。这样4颗裸片的产品在性能上无疑是要强于1颗裸片(裸片型号相同)的产品。

在AMD一代EPYC处理器的开盖视频中我们可以发现,每颗裸片之间都有着毫米级肉眼可见的间距。苹果所做的则是在此基础上更近了一步,将两颗裸片“贴脸”封装,使得两颗裸片之间的连线变得更短。并且由于之前设计M1 Max时预留的接口,两颗裸片之间可以用更快的速度进行通讯,最终实现了两颗裸片之间2.5TB/s的连接带宽。

节约成本

虽然大家都知道芯片的流片成本很高,但其实只是流片的门槛成本高。当一款芯片开始大批量生产之后,边际成本是比较低的。举个例子来说,造芯片就像是造塑料洗脸盆。洗脸盆的生产线搭建起来很贵,但你把洗脸盆的生产线搭建起来之后,后面所需的材料成本就很低了。

如果这时候你想生产另一种尺寸的塑料洗脸盆,那你就需要修改生产线甚至重新搭建一条新生产线,这样就贵了。

所以对于此时的苹果来说,如果单独设计另一个更大尺寸的芯片,而且还是5nm的芯片,成本是非常高的。所以苹果最终的选择是将两颗M1 Max封装到一起,这样新产品可以继续利用原有M1 Max的生产线,只需要最后将裸片进行特殊封装就可以了。

这就像是一个生产塑料洗脸盆的厂商,原来是一个洗脸盆装一个纸箱,现在变成了两个洗脸盆装一个纸箱,此时只需要重新订购更大尺寸的纸箱就可以了。

另一方面,就是裸片的良率问题了。当裸片的面积越大时,良率就会越低。

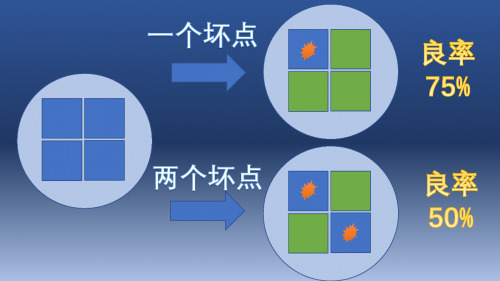

假设一块小晶圆上面最多可以生产4块M1 Max,如图所示当晶圆上出现一个“坏点”时,最终就只能生产出3块M1 Max,这时良率是75%。而当出现两个“坏点”时,最终就只能生产出2块M1 Max,这时良率是50%。但如果直接生产M1 ULTRA这样大面积的裸片会发生什么呢?

这时同样的一个晶圆上最多可以生产2块M1 ULTRA。如图所示当晶圆上出现一个“坏点”时,最终就只能生产出1块M1 ULTRA,这时良率是50%。而当出现两个“坏点”时,最终就只能生产出0块M1 ULTRA,这时良率是0%。

由此可以看出当裸片的面积越大,其它条件相同时,良率就会越低。反之如果把一个大芯片分成两个小芯片做,良率就会提高。良率提高了,相应成本也就省下来了。

结语

在文章的最后,我有一些想法和补充的信息,在此分享给大家。

1、苹果作为一家Fabless(无晶圆厂模式)公司,对于半导体工艺发展进入瓶颈这件事是无能为力的。只能等待台积电、三星等晶圆厂研发出更先进的工艺。

2、在工艺进入瓶颈之后,芯片性能如果再想提升,苹果这种做法是简单粗暴而且有效的。

3、Die-to-Die技术的本质是将一个大的Die(裸片)分成几个小的Die(裸片)来做,这样成本更低。

4、现在业界也有这种设计的趋势,将原来一个大芯片拆成几个小芯片进行设计制造。

5、这种技术并不是完美的,比如会引入额外的散热负担。而通过主板PCB连接两颗CPU这种方式,散热问题会小很多。毕竟间距够大,可以通过多个散热器解决。

6、基于此种情况进行一个预测,M1 ULTRA的实际性能不会是M1 Max的2倍,但应该能超过1.5倍。毕竟苹果有“单管压i9”的前例在,散热问题处理得怎么样还是要等真机发售之后看。