小到晶体管栅极开关时等效尺寸都不一样了。

从 20 世纪 50 年代集成电路问世以来,硅晶体管像摩尔定律预测的那样逐渐缩小。微芯片上的晶体管数量越来越多,计算能力也越来越高。

然而,近年来,晶体管的尺寸正在迅速接近极限。栅极长度很快就将无法再缩小,摩尔定律即将终结的「唱衰」之音在芯片行业泛起。

在所有晶体管中,电流从源极流向漏极,这种电子流动由栅极控制,栅极根据施加的电压打开和关闭。因此栅极的长度是晶体管尺寸的关键标志。在 5 nm 以下,由于隧穿效应(一种量子物理现象),硅不再能够控制电子从源极到漏极的流动。

最近,科学家们开始探索用于下一代电子产品的二维材料,包括由单层碳原子组成的石墨烯,以及两层硫原子中间夹一层钼原子组成的二硫化钼(MoS2)。例如,在 2016 年,科学家们使用碳纳米管和二硫化钼制造了一个栅极长度仅为 1 nm 的晶体管,但这还不是极限。

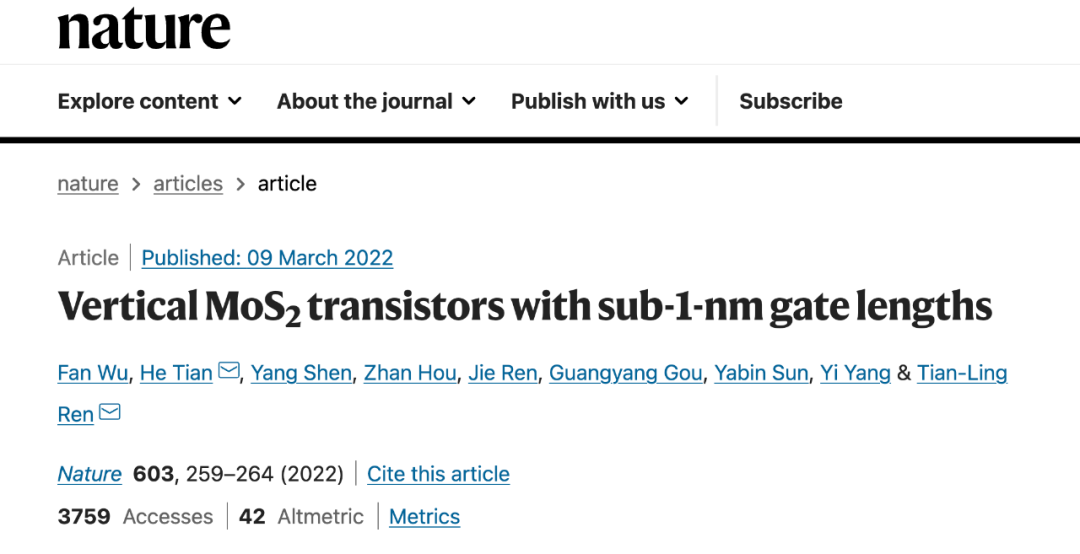

近日,清华大学集成电路学院任天令教授团队在小尺寸晶体管研究方面取得重大突破,首次实现了具有亚 1 纳米栅极长度的晶体管,并具有良好的电学性能。这项研究以《具有亚 1 纳米栅极长度的垂直硫化钼晶体管(Vertical MoS2 transistors with sub-1-nm gate lengths)》为题,刊登于最新一期《Nature》杂志。

论文链接:https://www.nature.com/articles/s41586-021-04323-3

论文通讯作者为清华大学集成电路学院任天令教授和田禾副教授,共同第一作者包括清华大学集成电路学院 2018 级博士生吴凡、田禾副教授、2019 级博士生沈阳,其他参加研究的作者包括清华大学集成电路学院 2020 级硕士生侯展、2018 级硕士生任杰、2022 级博士生苟广洋、杨轶副教授和华东师范大学通信与电子工程学院孙亚宾副教授。

「我们已经实现了世界上栅极长度最小的晶体管,」任天令表示。这种晶体管的栅极长度仅约三分之一纳米宽,大约相当于单层碳原子的厚度。

任天令教授。

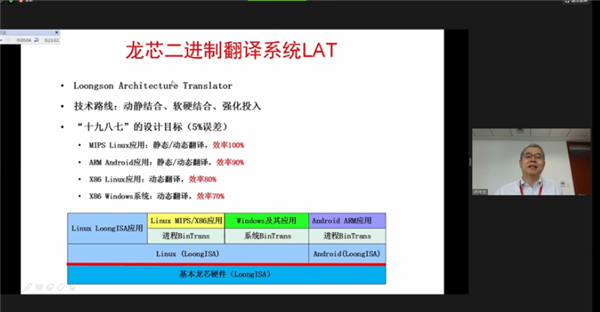

任天令教授。要想理解这种新设备,你可以想象楼梯的两个台阶,较高的台阶顶部是源极,较低台阶的顶部是漏极,两者均由钛钯金属触点制成。楼梯的截面作为连接源极和漏极的电子沟道,它由二硫化钼制成。该截面之下是一层薄薄的电绝缘二氧化铪。

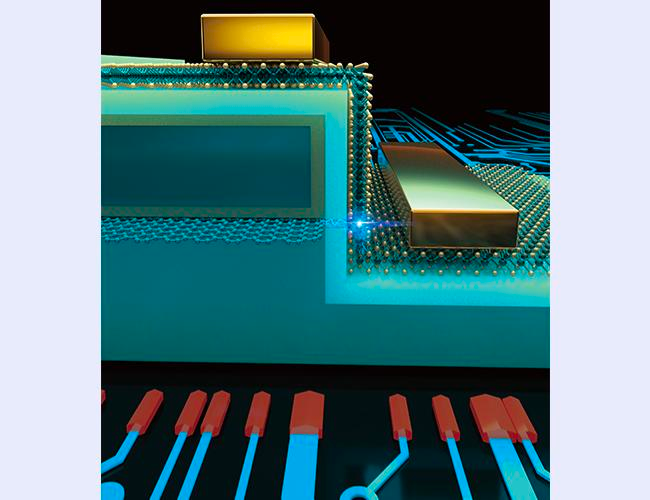

图 1:亚 1 纳米栅长晶体管结构示意图。亮点代表晶体管的栅电极。

图 1:亚 1 纳米栅长晶体管结构示意图。亮点代表晶体管的栅电极。在更高的那级台阶内部,是一个多层三明治结构。底层是一片石墨烯,由单层碳原子组成;在它之上是一块覆盖着氧化铝的铝块,使石墨烯和二硫化钼几乎完全分离,除了在更高台阶的垂直侧有一个薄薄的间隙。较高和较低的两级台阶都位于 5cm 硅晶片的二氧化硅层上。

研究团队巧妙地利用石墨烯薄膜超薄的单原子层厚度和优异的导电性能作为栅极,通过石墨烯侧向电场来控制垂直的二硫化钼沟道的开关,从而实现等效的物理栅长为 0.34nm,与石墨烯层宽度相同。

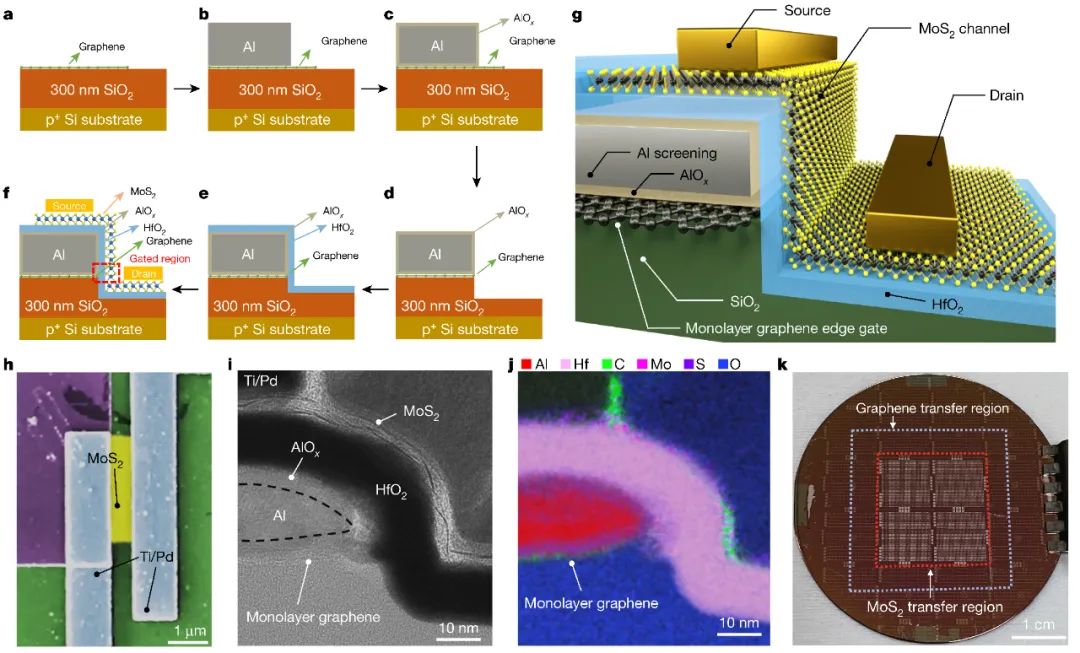

通过在石墨烯表面沉积金属铝并自然氧化的方式,该研究完成了对石墨烯垂直方向电场的屏蔽,并使用原子层沉积的二氧化铪作为栅极介质、化学气相沉积的单层二维二硫化钼薄膜作为沟道。具体器件结构、工艺流程、完成实物图如下图所示:

图 2:亚 1 纳米栅长晶体管器件工艺流程,示意图,表征图以及实物图。

图 2:亚 1 纳米栅长晶体管器件工艺流程,示意图,表征图以及实物图。「在未来,人们几乎不可能制造小于 0.34nm 的栅极长度,」任天令教授表示。「这可能是摩尔定律的最后一个节点了。」

2021 年,另一个研究小组公布了他们研究的一种垂直晶体管,它使用二硫化钼制成,栅长为 0.65 nm。但清华的这项新工作将栅极的尺寸限制进一步推至「仅一层碳原子的厚度」,纽约州立大学布法罗分校的纳米电子学科学家 Huamin Li 说。在相当长的一段时间内,要打破这一纪录是很困难的。

在晶体管中,当施加电场时,栅极开和关的状态通常存在长度上的差异,但在更大的范围内,这种效应通常并不明显。在这个新装置中,当有电压施加到栅极上使其切换到关闭状态时,栅极的等效长度变成了 4.54 纳米,这一差异可以证明是一个优势。

「在关闭状态下,具有较高电阻的长沟道将有助于防止泄漏电流,」Li 说,「相反,在导通状态下,具有较小电阻的较短沟道将提高导通状态下的电流密度。」

这项工作推动了摩尔定律进一步发展到亚 1 纳米级别,同时为二维薄膜在未来集成电路的应用提供了参考依据。

未来,清华的研究人员计划用他们的新型晶体管创造更大规模的电路。任天令说:「下一个目标是制造 1-bit CPU。」不过,这个目标也充满挑战,其中一个可能的挑战是制造更高质量、更大面积的二硫化钼,以及这种材料目前居高不下的成本。

总而言之,「这项原型工作是继 FinFET 技术的发展之后,人类探索晶体管垂直架构的新尝试,」Li 说,「希望这将激发更多的创造性想法,以充分探索 2D 材料的潜力,并将摩尔定律推广到高性能节能纳米电子领域。」