原标题:Synopsys全球首发PCIe 6.0完整方案:用上5nm工艺 来源:快科技

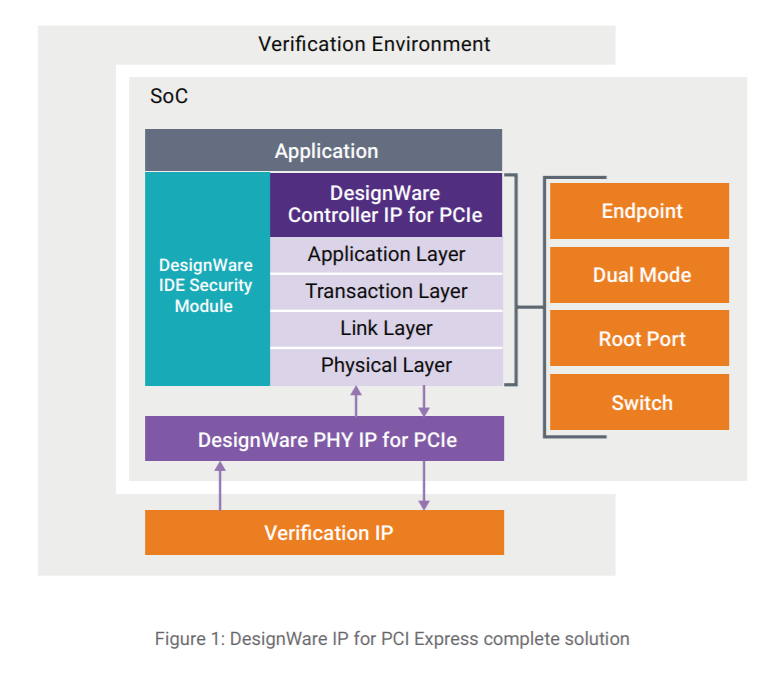

PCIe 4.0还在普及阶段,PCIe 5.0尚未到来,PCIe 6.0标准规范还没完成,厂商们就已经迫不及待出方案了。Synopsys(新思科技)宣布,推出全球首个完整的PCIe 6.0 IP方案,包括控制器、PHY物理层、验证IP,可供PCIe 6.0 SoC设计早期开发之用。

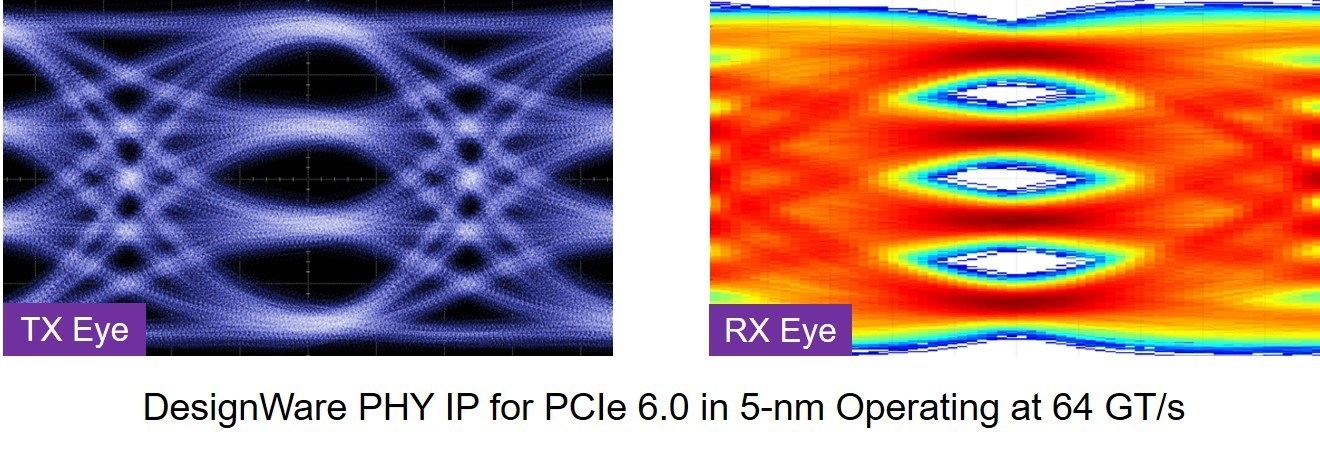

它基于Synopsys广受好评的DesignWare IP PCIe 5.0方案,完整支持PCIe 6.0标准特性,包括64GT/s PAM-4信号调制、FLIT模式、L0p低功耗模式等等,可满足HPC高性能计算、AI、存储SoC等应用领域对于延迟、带宽、能效的各种需求。

为了实现吞吐量的最大化、延迟的最小化,Synopsys PCIe 6.0控制器采用了“MultiStream”(多流)架构,性能可达单流架构的最高2倍,并且还有1024-bit宽度架构,可以在关闭1GHz时序的同时,达到64GT/s x16的高带宽,还优化了多数据源、多虚拟通道环境。

此外,新方案使用了独特的自适应DSP算法,支持早期SoC开发,优化模拟和数字均衡,无论何种通道下都能获得最佳能效,并且基于专利诊断功能,可确保几乎零宕机时间。

值得一提的是,PHY物理层还使用了先进的5nm工艺,搭配独特的模拟和DSP技术,可将功耗降低20%。

Synopsys PCIe 6.0 IP方案中的验证IP现已可用,控制器、PHY物理层计划在今年第三季度提供早期试用。

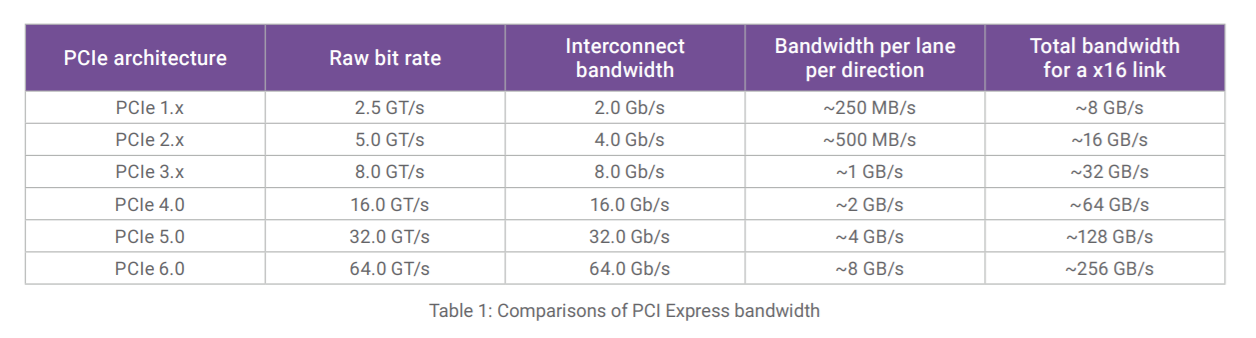

PCIe 6.0标准规范目前还在制定中,计划在今年正式发布,按照传统继续让I/O带宽翻番达到64GT/s,应用到实际中,PCIe 6.0 x1单向实际带宽8GB/s,PCIe 6.0 x16单向带宽128GB/s、双向带宽256GB/s。

PCIe 6.0将延续PCIe 3.0时代引入的128b/130b编码方式,但加入全新的脉冲幅度调制PAM4,取代PCIe 5.0 NRZ,可以在单个通道、同样时间内封包更多数据,以及低延迟前向纠错(FEC)和相关机制,以改进带宽效率。