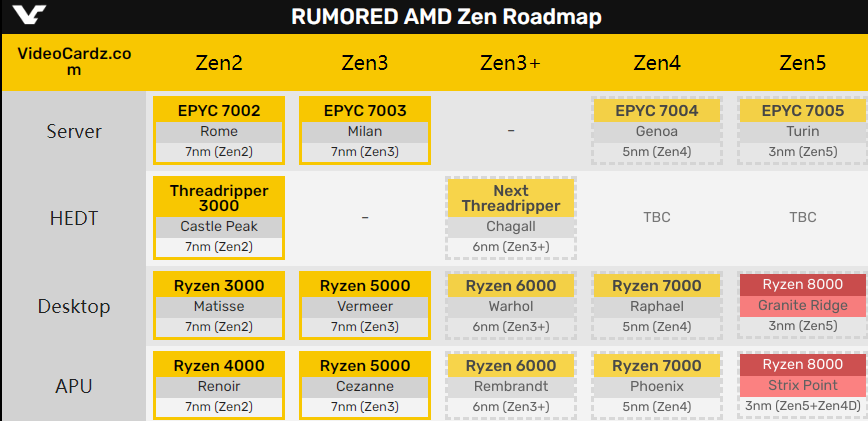

原标题:AMD Zen4细节泄露:5nm+7nm混合、集成RDNA2 GPU 来源:快科技

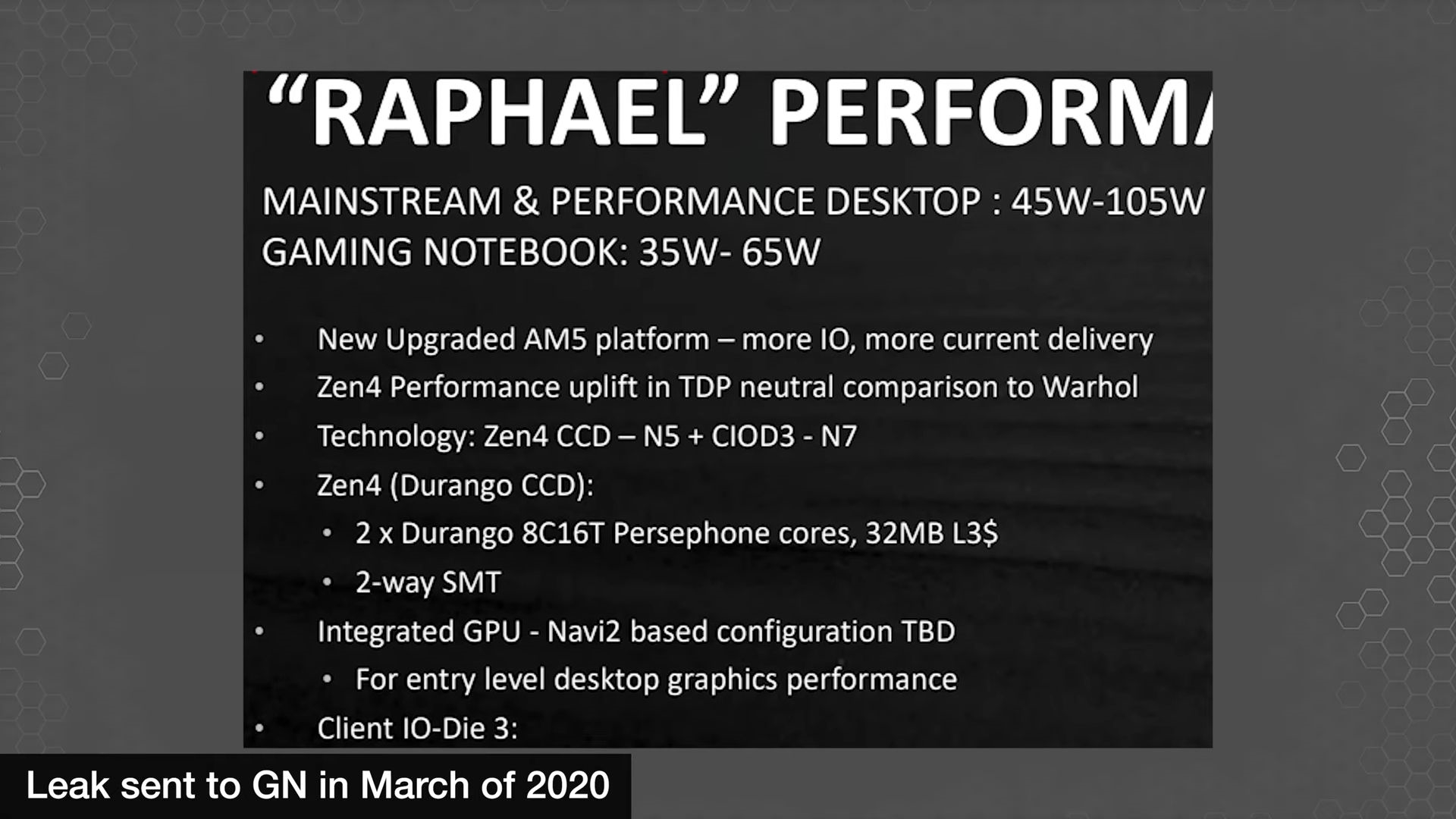

5nm Zen4架构的锐龙、霄龙处理器都将在明年登场,而在那之前,今年底不是Zen3+,就是Zen3穿马甲。外媒披露了一份AMD内部资料,时间是今年3月,列出了Zen4架构首款锐龙处理器“Raphael”(拉斐尔)的详细情况,预计将会命名为锐龙7000系列。

它依然采用chiplest小芯片设计,计算核心与输入输出分离,分别叫做CCD、CIOD3,制造工艺分别是台积电N5 5nm、N7 7nm。

CCD部分代号“Durango”,每个最多8核心16线程、32MB三级缓存,和现在的Zen3完全一样,两个组成最多16核心32线程、64MB三级缓存。

之前有消息称AMD在测试24核心型号,但是否推出还要看各方面情况。

同时入门级型号会集成GPU,终于升级到RDNA2架构,但具体规格配置待定。

整体采用AM5封装接口,热设计功耗方面中高端桌面型号45-105W,比现在下探20W,笔记本型号35-65W,比现在上探20W。

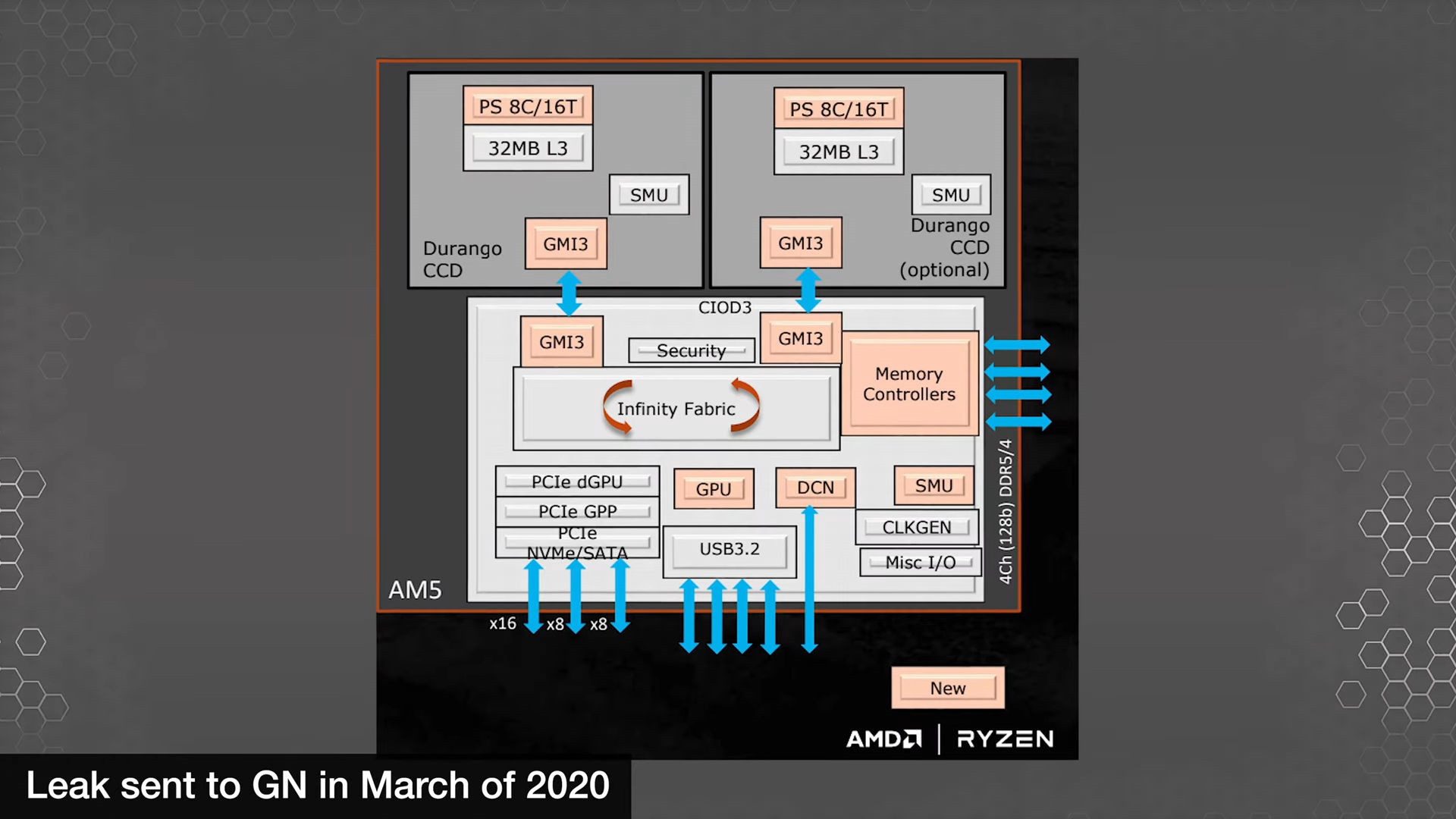

另一张幻灯展示了Raphael处理器的内部结构。

CCD、CIOD3之间通过新的GMI3总线相互连接,后者集成新的内存控制器(DDR5)、GPU图形核心。

以往的锐龙APU都是单芯片设计,这将是第一次采用chiplet多芯片设计。

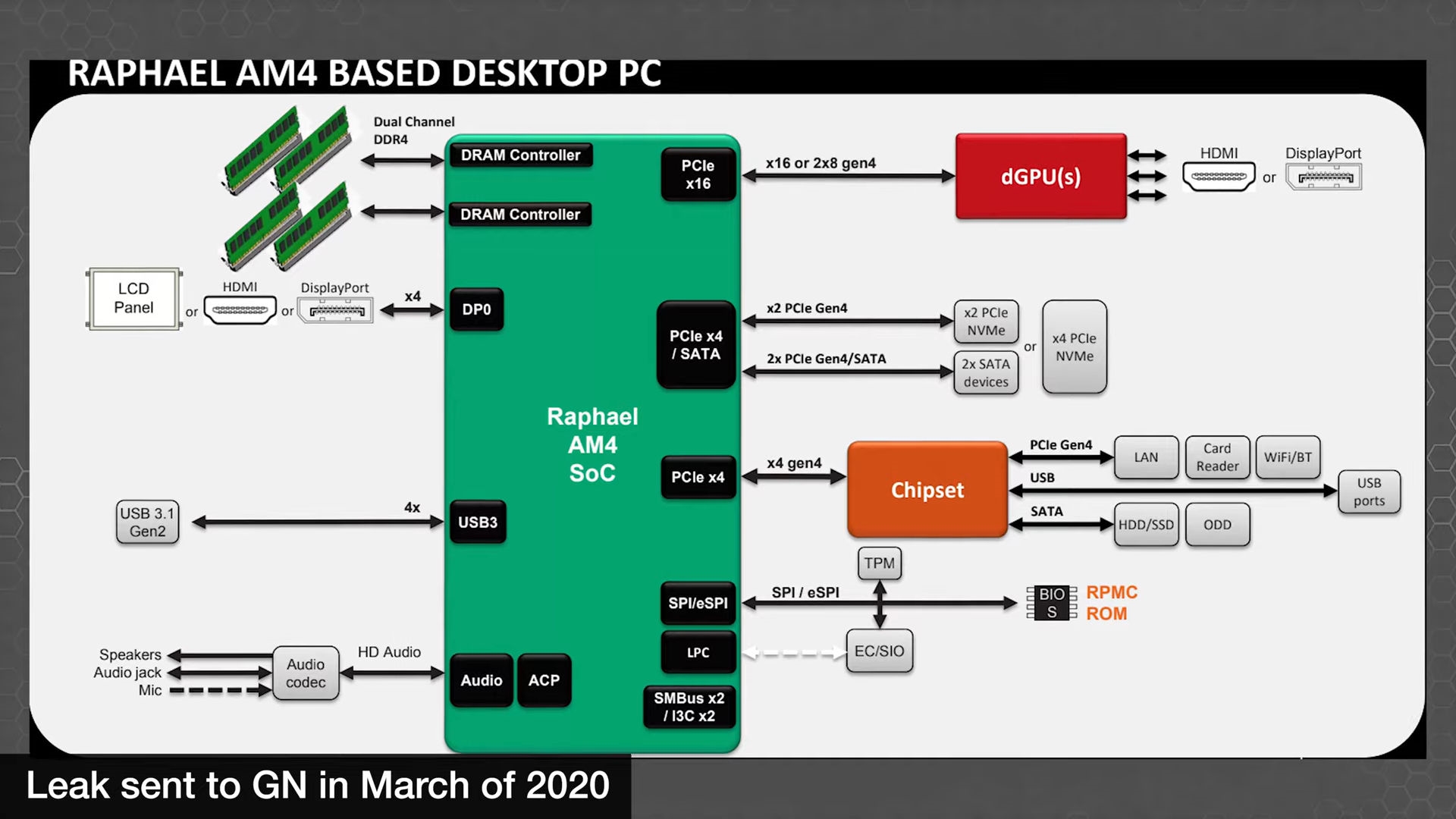

最后是Raphael平台架构图,确认继续支持PCIe 4.0,通道数量从24条增加到28条,其中16条分给独立显卡、4条连接PCIe/SATA SSD、4条连接芯片组(600系列)之后再扩展支持网卡、读卡器、Wi-Fi(蓝牙)、USB、硬盘、光驱等等。

不过奇怪的是,之前说法称Zen4架构不会再兼容DDR4,但这里图上依然标注DDR4,而且接口还是AM4,不知道是笔误还是回事儿。

再往后的Zen5架构的锐龙8000系列,也有消息传出,台积电3nm工艺,同时集成Zen4D组成大小核心混合架构,最多8+4的组合,并有新的缓存体系、内存子系统。