原标题:台积电打响先进封装“攻坚战” 来源:爱集微

集微网消息,如果说此前封装技术还被认为是归于产业链后端流程的技术,现在“时代变了”。台积电在官网关于3D封装如此介绍,计算工作的负载在过去十年中的发展可能比前四个十年都要大。云计算、大数据分析、人工智能 (AI)、神经网络训练、人工智能推理、先进智能手机上的移动计算甚至自动驾驶汽车,都在推动计算向极限发展。

在这过程中,封装技术也被推向了创新的前沿,其对产品的性能、功能和成本有着至关重要的影响。也因此,封装技术不再是后端流程的“专属”,晶圆代工巨头也开始纷纷入局。

晶圆代工龙头台积电在先进封装的超前布局

近日,因为疫情因素,行业热点大会Hot Chips 33 在线上展开。台积电Pathfinding for System Integration副总经理余振华主要分享了台积电的chiplet(小芯片)和3D封装技术。

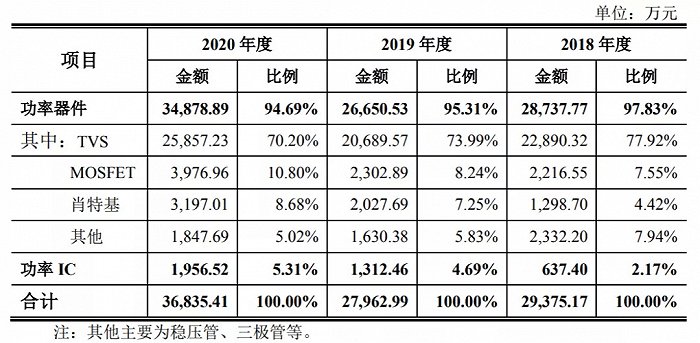

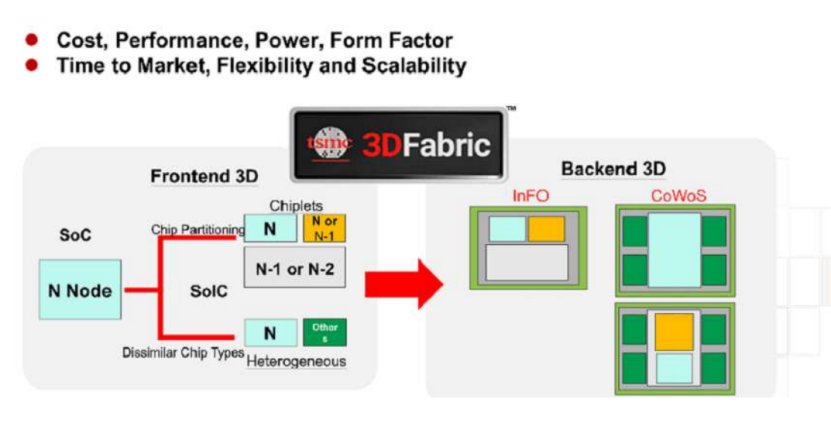

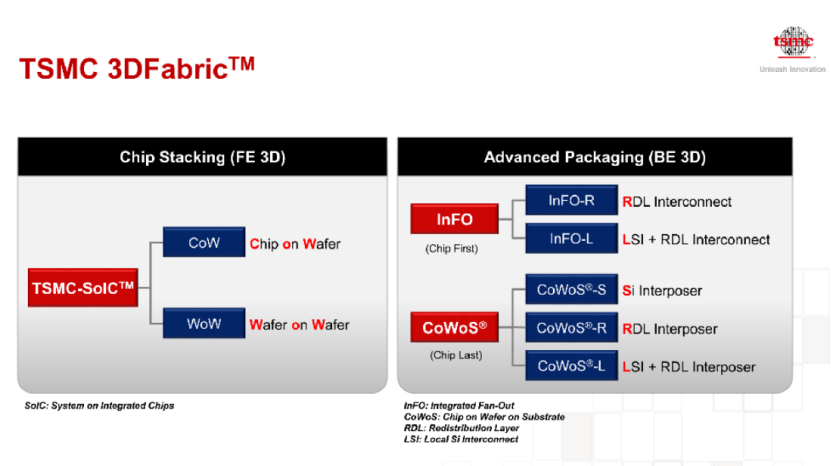

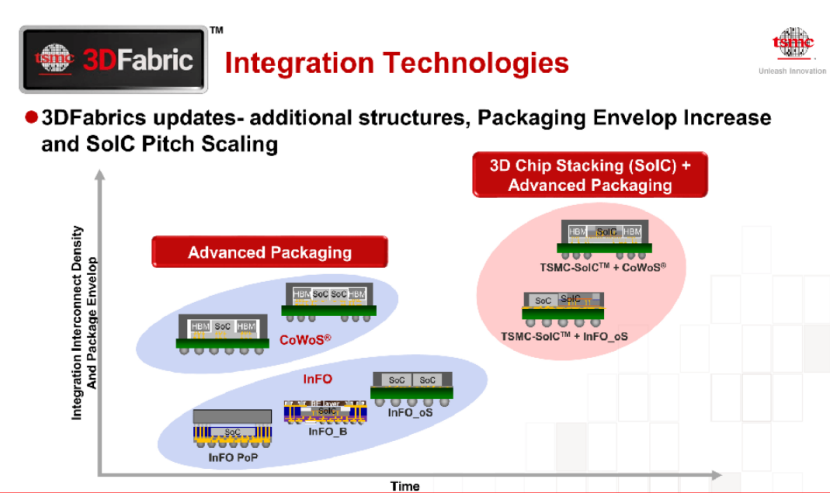

余振华介绍了台积电3D Fabric技术平台的细节,该技术平台包含台积电前端芯片堆叠SoIC技术和后端先进封装CoWoS和InFO技术。

其实,早于2020年,台积电就表示已整合旗下 SoIC、InFO 及 CoWoS 等 3D IC 技术平台,并命名为“3D Fabric”。

根据PPT展示,SoIC技术包括CoW和WoW两种键合方式。根据互连方式的不同,InFO可以分为InFO-R和InFO-L两种;CoWoS则分为CoWoS-S、CoWoS-R和CoWoS-L三种。

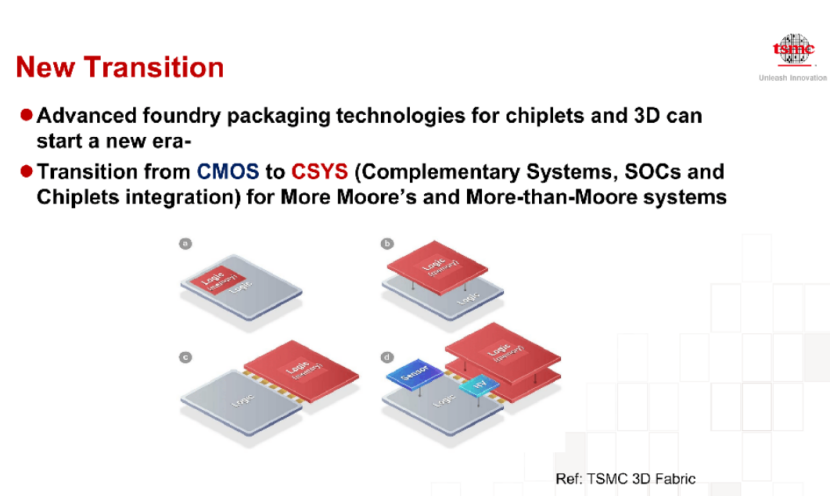

余振华认为,封装领域正在发生新的变化,主要包括以下两点:

-小芯片和 3D先进封装技术将会开启一个新时代;

-从 CMOS 转变到 CSYS(互补系统、SOC 和小芯片集成),可以实现从摩尔到超越摩尔的过渡;

台积电还对3D Fabrics进行了更新。随着时间发展,台积电的先进封装技术也会从InFO和CoWoS变为SoIC+InFO、SoIC+CoWoS的方式。台积电还介绍了包括拥有针对移动AP的InFO_B (Bottom Only)技术和针对HPC的chiplet集成技术InFO-R/oS的更新。

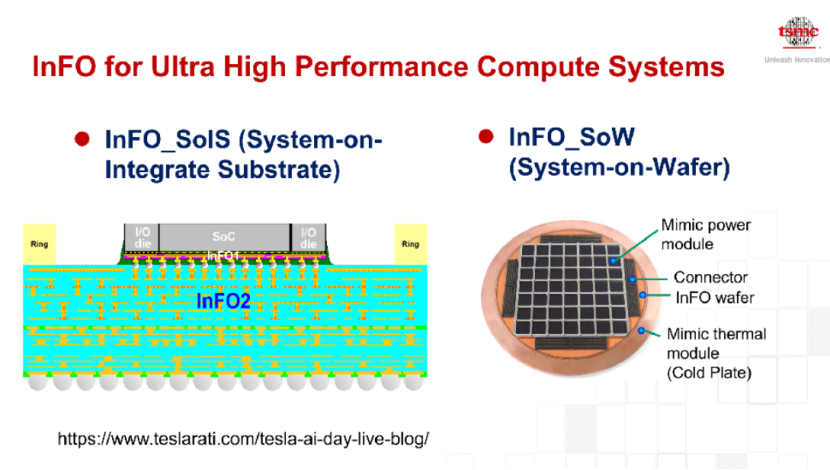

面向超高性能的计算系统,台积电也提供了InFO_SoIS和InFO_SoW两种技术。并且,该技术可以确定使用在tesla最新的AI芯片上。

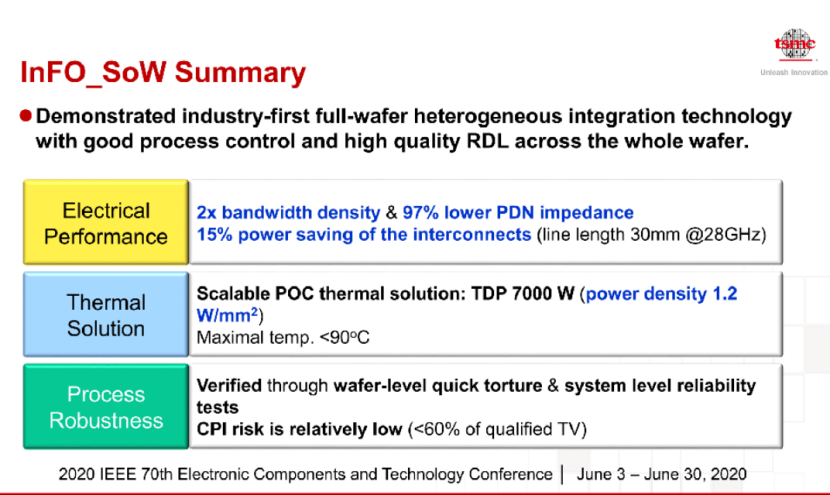

值得一提的是,InFO_SoW是业界第一个全晶圆异质集成技术,在带宽密度和PDN阻抗上具有显著优势。

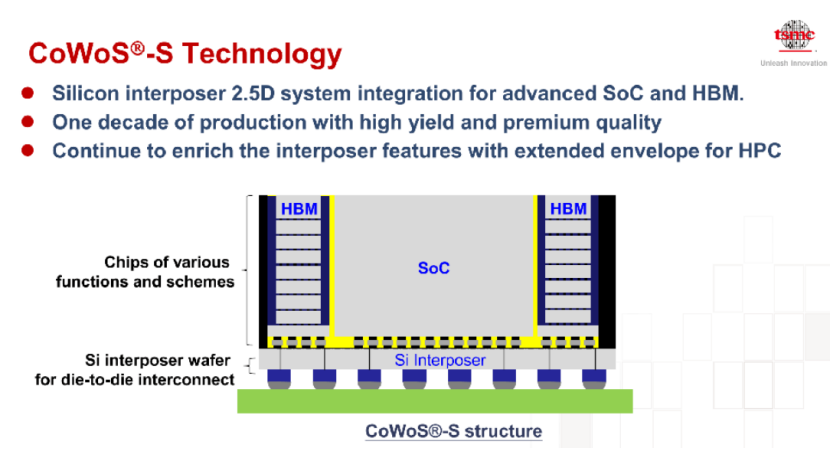

接下来是CoWoS-S封装技术。该技术已经量产超过十年,且拥有极高的良率和质量,能够为先进的SoC和HBM集成提供友好支持。

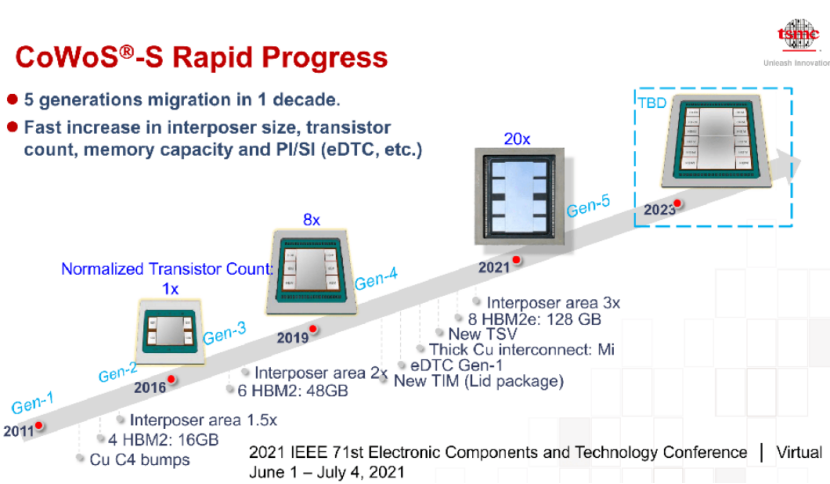

台积电预计将在今年晚些时候发布第5代 CoWoS-S 封装解决方案,这将使晶体管数量比第 3 代封装解决方案增加 20 倍。新封装将增加3倍的中介层面积、8 个 HBM2e 堆栈(容量高达128 GB)、以及提供全新的TSV解决方案。

到第 6 代,新封装将拥有更大的掩模版面积,以集成更多的小芯片和更多的 DRAM 封装。

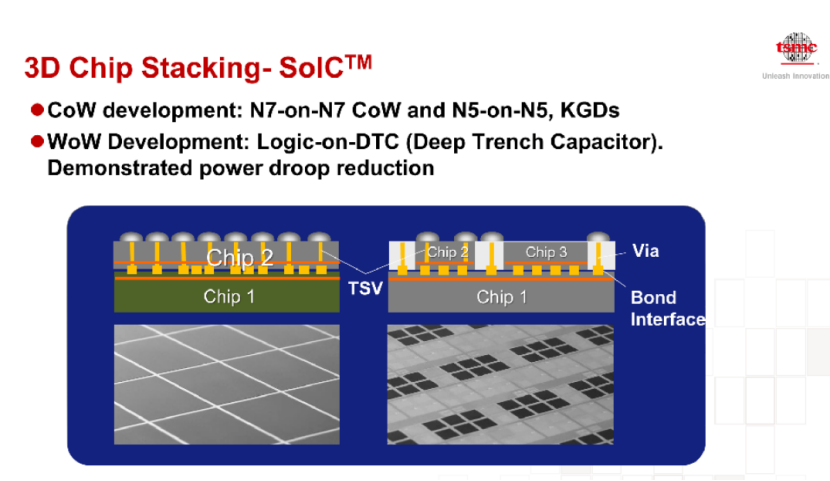

接着,余振华介绍了台积电3D芯片堆栈——SoIC。按照规划,台积电在CoW方面正在开发N7-on-N7和N5-on-N5等;WoW方面,台积电则在开发Logic-on-DTC(Deep Trench Capacitor)。

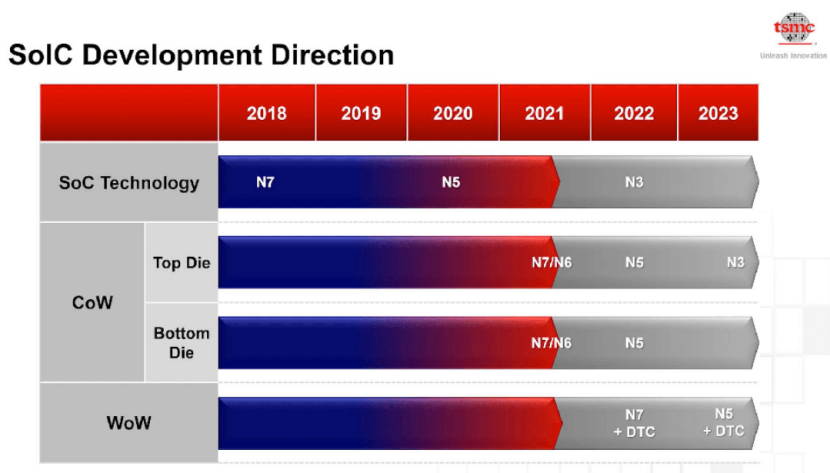

此外,台积电也公布了其SoIC研发进度。当前,CoW和WoW都为N7/N6工艺,预计明年将会实现基于N5工艺。

会上,还透露了台积电芯片互连路线图,预计将于2035年前实现1μm以内的SoIC互连。

在介绍完了封装技术外,余振华还介绍了台积电的全新异构集成技术,包括现金的热解决方案和硅光集成。

余振华最后总结了以下三点内容:

1.台积电 3D FabricTM技术平台将继续扩大封装规模,减少3D堆叠互连密度,从而提升功耗表现。

2.利用3D Fabric集成创新的SiPh组件 (COUPE) 可进一步增强系统性能;

3.新的微型冷却系统-ISMC和DWC也可以解决热能瓶颈,以实现更多的3D堆叠。

先进封装未来可期

近日,中国台湾工业技术研究院研究总监杨锐预测,台积电将再主导芯片制造行业五年,此后3D封装将成为主要工艺挑战。

其实,除了台积电之外,英特尔和AMD均在本次大会上提到了3D封装技术。此外,另一家行业巨头三星同样也在加强部署3D封装技术。为何3D封装技术会成为行业巨头们“不约而同”的选择?

在过去的十年里,各种计算工作量发展迅速,但摩尔定律却面临着失效的风险。面对更多样化的计算应用需求,为了将更多的功能“挤”进同一个芯片中,先进封装技术成为持续优化芯片性能和成本的关键创新路径。

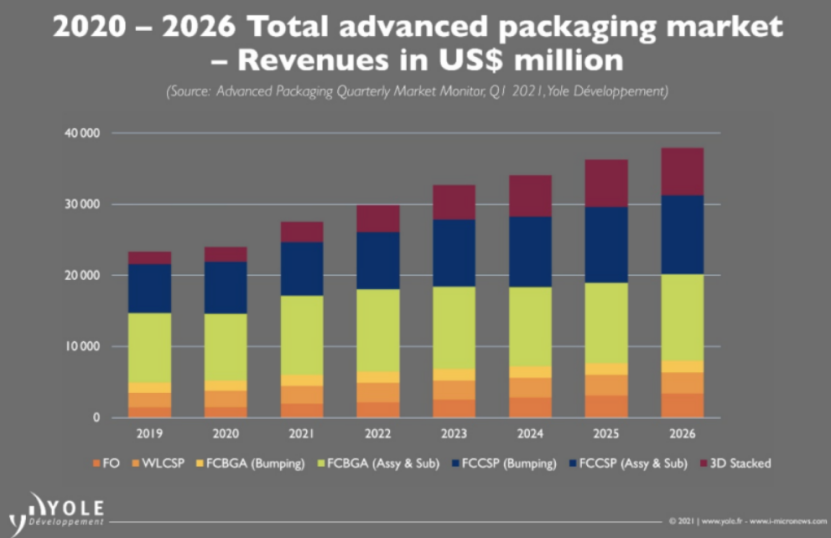

由此,也带动了先进封装市场的荣景。根据Yole Developpement最新的数据,2020年至2026年,先进封装市场复合年增长率约为7.9%。到2025年,该市场营收就将突破420亿美元,这几乎是传统封装市场预期增长率(2.2%)的三倍。

其中,3D封装在集成度、性能、功耗等方面更具优势,同时设计自由度更高,开发时间更短,是各封装技术中最具发展前景的一种。当前,随着高效能运算、人工智能等应用兴起,加上TSV技术愈来愈成熟,可以看到越来越多的 CPU、GPU 和存储器开始采用3D 封装。

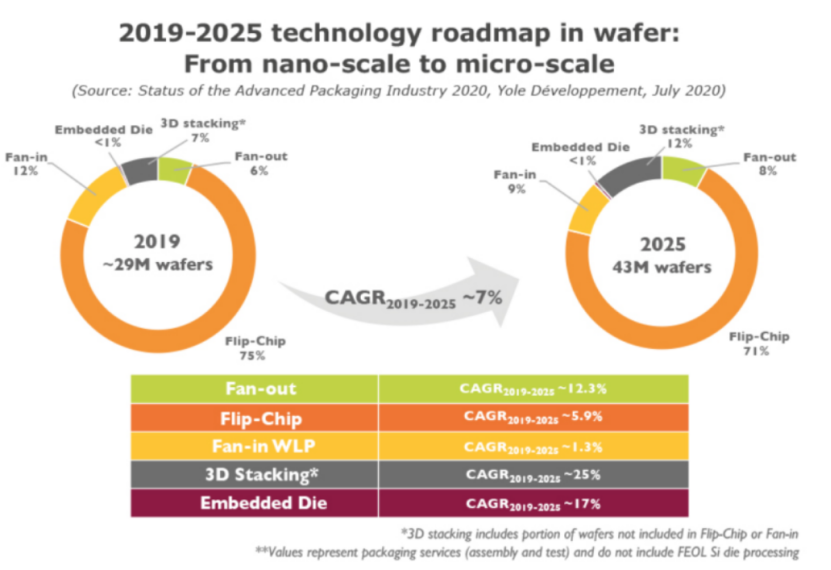

根据Yole、集微咨询综合整理,按晶圆数量(折合12英寸)来看, 2019 年约 2900 万片晶圆采用先进封装, 这一数字到 2025 年增长为 4300 万片,复合年均增长率为 7%。其中倒装技术占比最高,晶圆数量达3072万片,3D 封装增速最快,CAGR 约为 25%。

总结:随着行业巨头的涌入和超前布局,3D先进封装的未来已逐渐明朗。“后摩尔时代”,先进封装技术的未来值得期待。