原标题:英特尔公布尖端技术尝试延续摩尔定律,能否逆袭台积电?

图片来源:Pexels

图片来源:Pexels记者 | 彭新

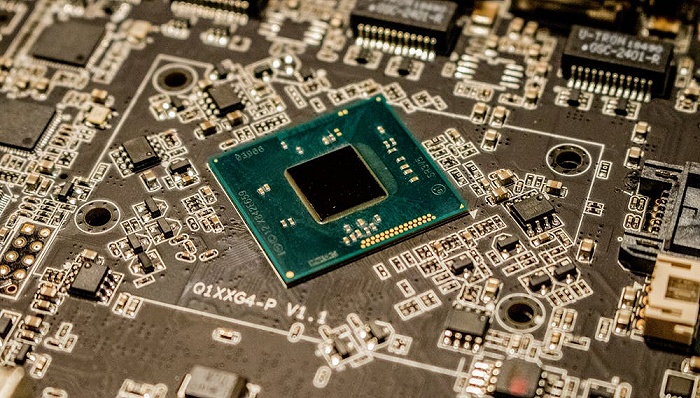

如何延续芯片行业的摩尔定律,一直是半导体公司所关注的焦点。

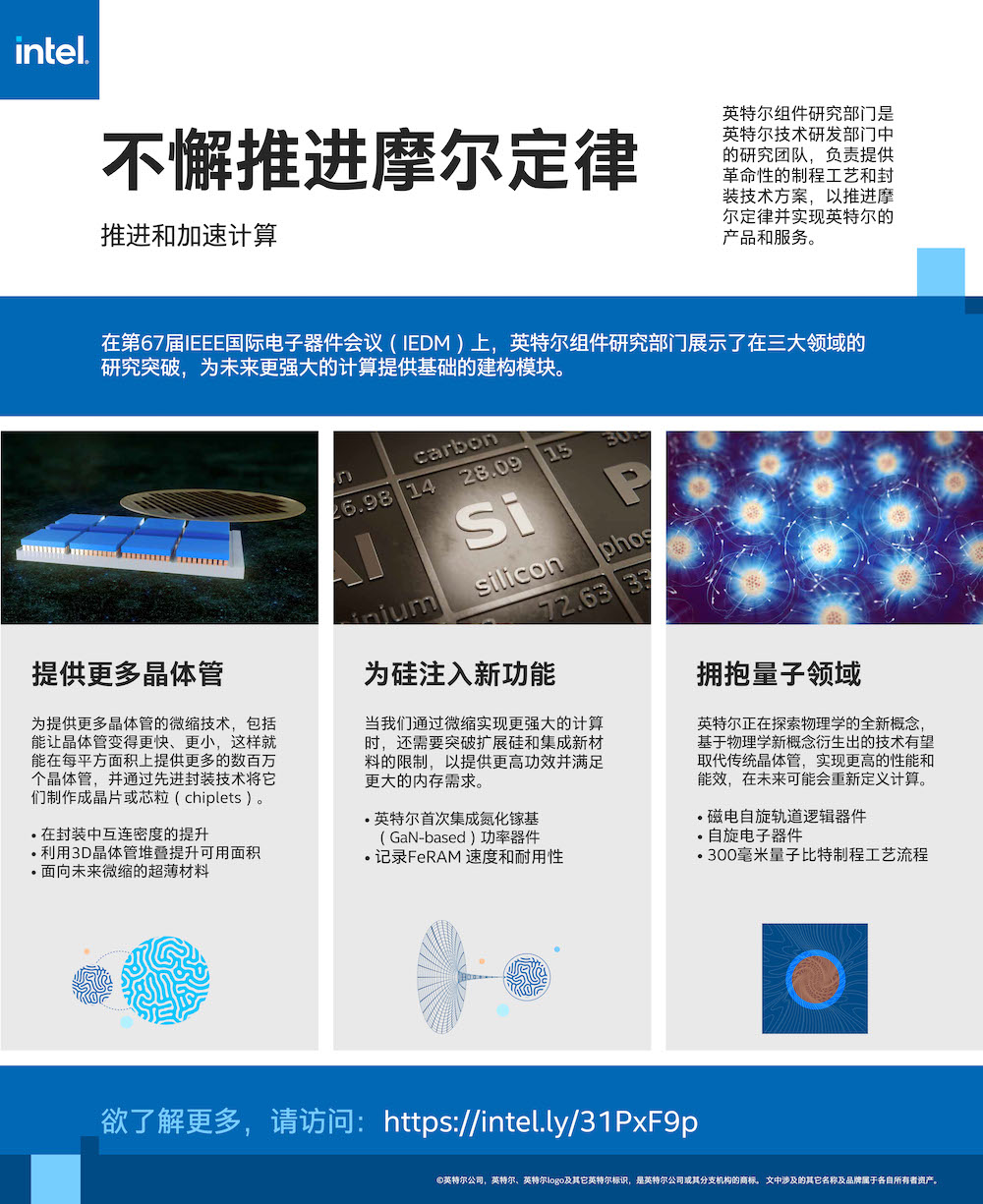

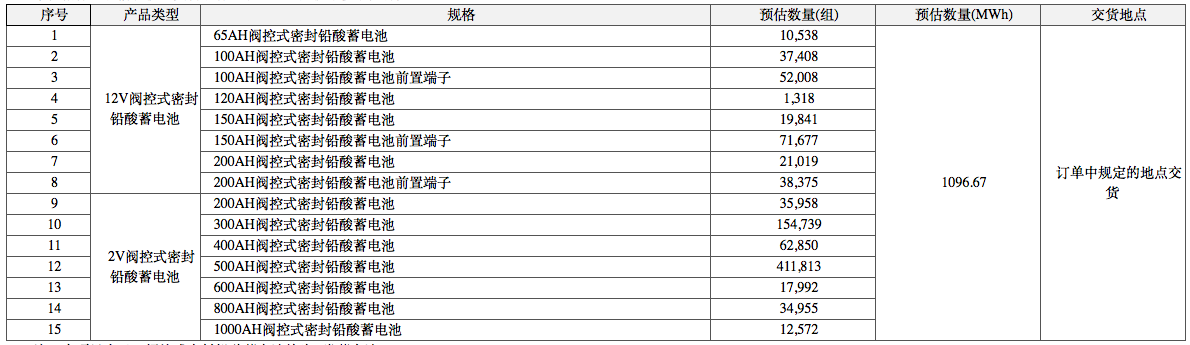

在12月11日至15日举行的2021 IEEE国际电子器件会议(IEDM)期间,芯片巨头英特尔公布多项尖端半导体开发前沿技术以推动摩尔定律,称将在芯片封装、功率器件和内存材料、尖端物理学三大领域进行创新。

“目标是封装中将密度提升10倍以上,将逻辑微缩提升30%至50%,并布局非硅基半导体。”英特尔方面表示。

此前尖端半导体开发竞争的核心是芯片制程大小。所谓制程,指的是芯片中晶体管线宽的大小,制程越小,单个芯片上就能容纳越多的电路元件,芯片的性能越强、功耗越低。目前芯片制程的领先产品为台积电和三星量产的5纳米芯片,两家企业计划在2025年启动2纳米芯片的量产。美国IBM于5月宣布已成功进行2纳米芯片的试制。

在先进制程竞争中掉队的英特尔也在加快推进研发,以期追上竞争对手。但有观点认为,晶体管数目大约每18个月便会增加一倍的“摩尔定律”目前已接近物理极限,且难以覆盖成本。这无疑加大了英特尔追赶的难度。

英特尔要维持市场地位超越台积电,拓展新思路成为关键,从芯片制造角度来看,将芯片叠加起来的3D堆叠技术的重要性日趋增加。此前在设计上,英特尔将芯片分别负责功率、计算和存储的部分以平面形式排列,但新技术尝试以拼乐高积木的形式,将芯片以立体形式堆叠,通过先进封装技术将晶体管制作为芯粒(Chiplet)。

Chiplet近年成为芯片行业的关键词。传统系统单芯片的做法是每一个组件放在单一裸晶(Die)上,功能越多,硅芯片尺寸越大。Chiplet的特点是将大尺寸的多核心设计分散到个别微小裸芯片,如处理器、模拟组件、储存器等,再用立体堆栈的方式,以封装技术做成一颗芯片。

英特尔称,其新的3D堆叠、多芯片封装技术Foveros Direct可以让上下芯片之间的连接点密度提升10倍,而且每个连接点的间距小于10微米。新的封装方式在空间上提高芯片的晶体管密度,能在不缩小制程的情况下,将晶体管密度提升30%至50%,使摩尔定律重新生效。可以说,英特尔研发团队本次发表的研究成果中,最大的科技进步也是晶体管堆叠技术。

芯片封装技术以外,英特尔还将目光转向供应和控制电力的“功率半导体”和内存材料,试图探索芯片在硅以外的新方案。据英特尔介绍,通过在300毫米的晶圆上首次集成氮化镓基(GaN-based)功率器件与硅基CMOS,实现了更高效的电源技术。这为CPU提供低损耗、高速电能传输创造了条件,同时也减少了主板组件和空间。

英特尔的另一项芯片研究技术成果也依赖于材料进步:利用铁电材料性质的“铁电存储器(FeRAM)”迎来新进展,有望成为手机、电脑内存中常用的DRAM存储器下一代产品的关键材料。

FeRAM的特点是断电后不会丢失信息,耐用性增强。由于可在保存数据(运算到一半的数据等)的情况下切断电源,与现有存储芯片领域常用的DRAM和SRAM存储器相比,可大幅降低耗电量。而且FeRAM也可实现以纳秒(十亿分之一秒)为单位、与DRAM同等的高速运行。

此前受限于所用铁电物质特性的限制,该材料应用只局限于细分市场,但英特尔发布的成果显示,其记录了FeRAM材料高达2纳秒的极短访问时间和10亿次循环范围内的极高写电阻(耐用性),意味着FeRAM有望作为下一代嵌入式DRAM技术的可行方案。

在量子计算等尖端物理学领域,英特尔一方面基于尝试提升硅基半导体的量子计算性能,同时也在开发能在室温下进行高效、低功耗计算的新型器件。

该公司称,正探索物理学领域的新概念以推动半导体技术,进展包括首例常温磁电自旋轨道(MESO)逻辑器件,自旋电子器件以及芯片封装、功率器件和内存等。其中英特尔与比利时微电子研究中心(IMEC)在自旋电子材料研究方面的合作,利用电子自旋原理进行信息的传递、处理与存储,有望实现逻辑芯片和存储器功能的整合。

强化晶圆制造能力和追求先进工艺的路线,均需要坚实技术能力作为支撑,而这一次该公司技术团队推出了一系列“技术性武器”,或将帮助英特尔在2025年后追上主要竞争对手保持竞争能力。

此前,英特尔的新业务进展遇阻,传统业务也遭到打击。作为集芯片设计和生产为一体的IDM厂商,英特尔的先进工艺开发明显落后于对手台积电和三星。在基辛格(Pat Gelsinger)于今年初担任英特尔首席执行官之后,推出一系列在2025年重新赢得优势地位的商业发展规划。在战略上,基辛格强化了竞逐先进工艺节点的方向,并采取了对外开放晶圆代工产能、调整工艺节点命名方式等举措。此外,英特尔还在6月对组织架构进行了调整,新增两名技术背景的高管。