本文来自cnBeta

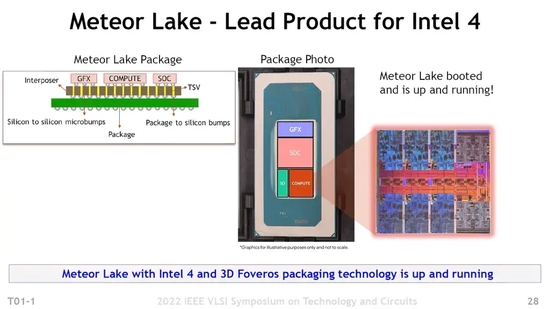

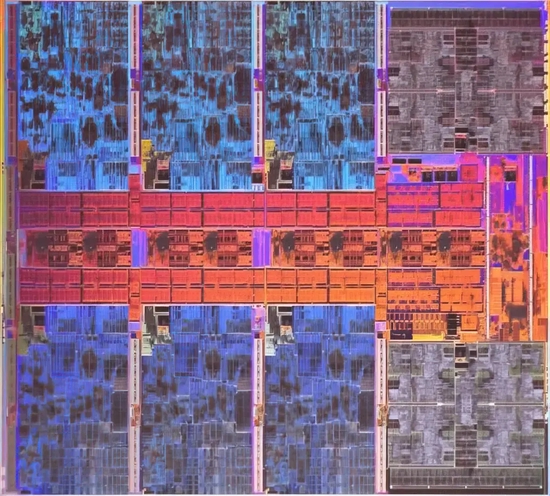

英特尔预估会在 IEEE VLSI 技术和电路研讨会期间展示第 14 代 Meteor Lake-P CPU,但看起来内核照片和细节在活动前几天已经泄露。本次活动中计划展示的 PPT 幻灯片已经被 Twitter 用户 @phobiaphilia 泄露,不过随后他删除了这些图片,所幸的是 Computerbase 设法获得了这些幻灯片。

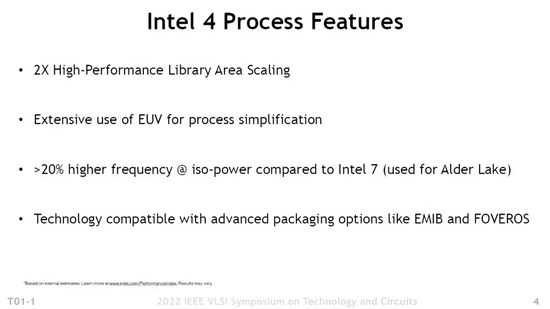

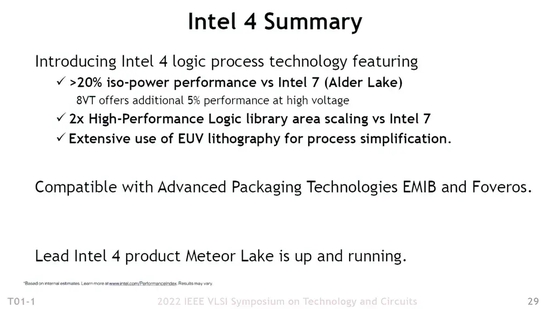

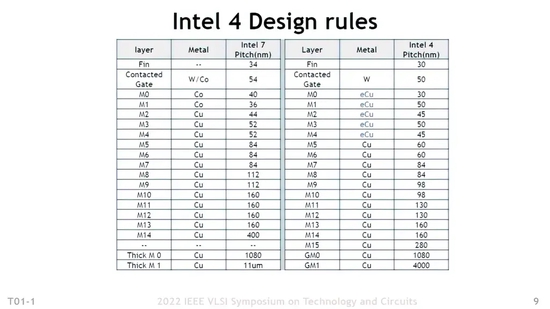

这些幻灯片讨论了被称为“Intel 4”的英特尔下一代工艺节点,它本质上是一种更名的 7nm 技术。第 14 代 Meteor Lake CPU 将利用“Intel 4”工艺节点,并提供两倍的 HPL(高性能库)缩放、用于简化工艺的 EUV、ISO 与英特尔 7 节点相比高 20% 的频率(由 Alder Lake 和Raptor Lake CPU)并提供与 EMIB 和 FOVEROS 等先进封装技术的兼容性。

总的来说,“Intel 4”流程节点的功能包括:

● 2 倍的 High-Performance Library Area Scaling

● 广泛使用 EUV 来简化工艺

● 和 Intel 7(用于 Alder Lake 和 Raptor Lake)相比,频率高 20%

● 技术兼容 EMIB 和 FOVEROS 等高级封装选项

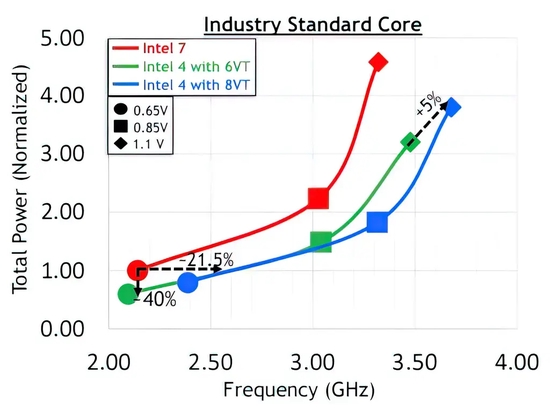

英特尔还谈到了其“Intel 4”节点的功率频率缩放,虽然有报道称第 14 代 Meteor Lake CPU 与基于“Intel 7”的芯片相比将出现时钟回归,但幻灯片显示频率跳跃在相同的功率下,“Intel 4”与“Intel 7”相比会更高。它可能不会反映在整个 7nm 产品系列中,但这至少是英特尔的目标。因此,在时钟方面,我们可以预期在相同功率水平下时钟速率提高 20%。

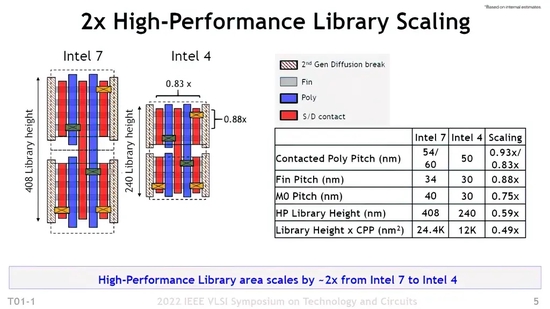

此外,幻灯片还详细介绍了第 14 代 Meteor Lake CPU 的“英特尔 4”节点的 2 倍 HPL 扩展。下一代 CPU 将具有:

● 接触式多晶硅间距 (nm):54/60 与 50(0.93x/0.83x 缩放比例)

● 鳍间距 (nm):34 对 30(0.88 倍缩放)

● M0 间距 (nm):40 对 30(0.75 倍缩放)

● HP 库高度 (nm):408 与 240(0.59 倍缩放)

● Library Height x CCP (nm2):24.4K与 12K(0.49 倍缩放)