选自IEEE

机器之心编译

编辑:杜伟

当单芯片处理器已达到极限,苹果和英伟达相继发布的芯片证明多芯片封装或许才是未来发展方向,但互连技术仍是一大难题和巨头角逐的主战场。

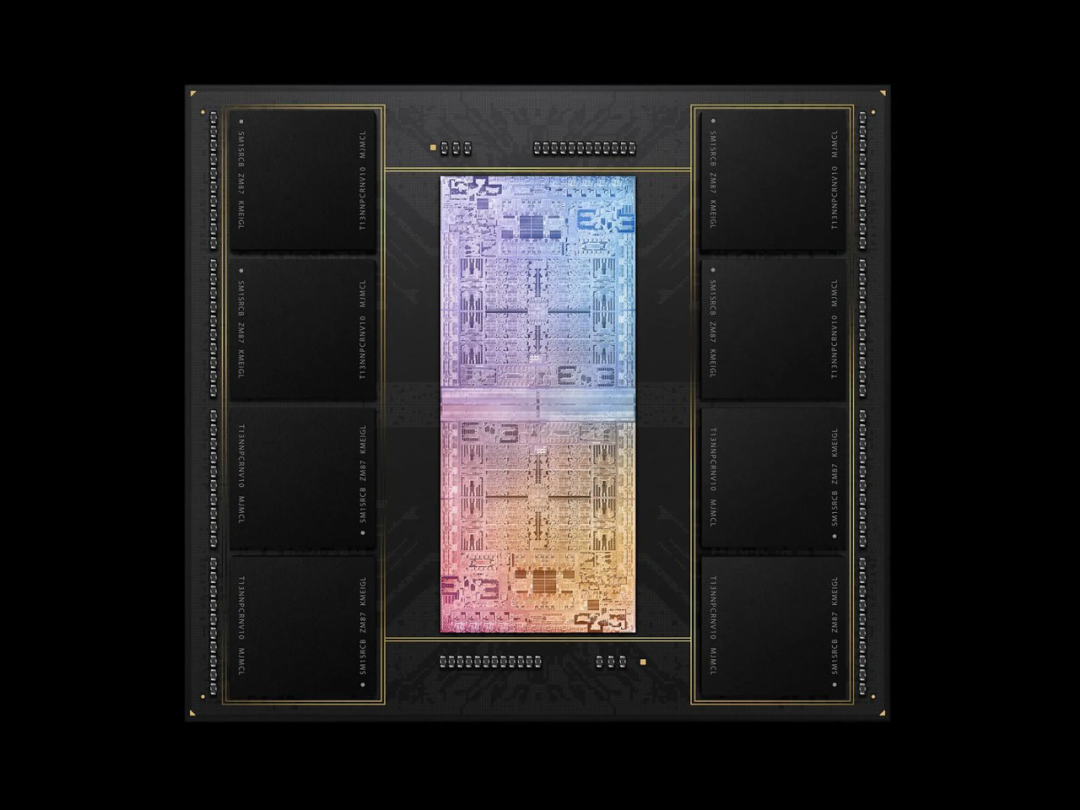

3 月 10 日,苹果在2022 年春季发布会上 M1 Max 芯片的升级版 ——M1 Ultra,创新性地采用了封装架构 UltraFusion,将两个 M1 Max 芯片的管芯相连,制造出了具有前所未有性能和功能的片上系统(SoC)。

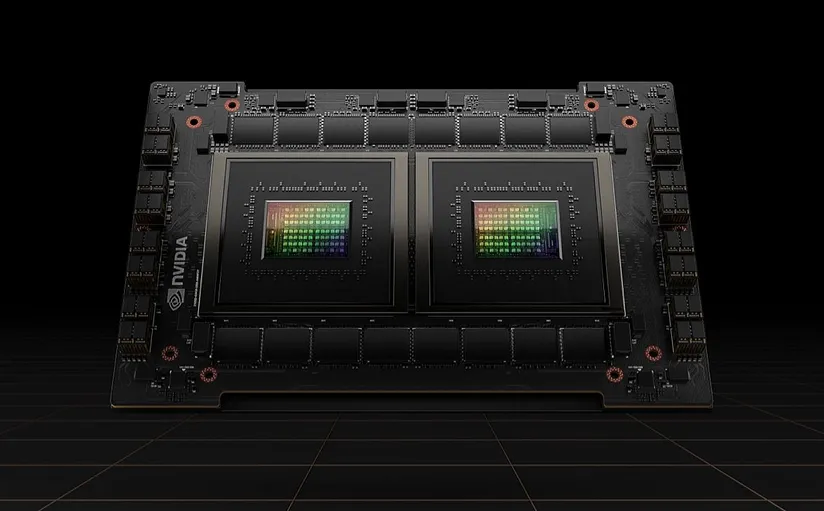

3 月 23 日,英伟达在 GTC 2022 大会上发布了类似的新闻。黄仁勋宣布推出首款面向 AI 基础设施和高性能计算的数据中心专属 CPU,其中新的 Grace Hopper 可以在同一块主板上两块并联,形成了一个 144 核的 Grace CPU 超级芯片,内存带宽为 1TB/s。

两家公司的芯片具有不同的目标市场。苹果瞄准消费者和专业工作站市场,而英伟达力图在高性能计算市场掀起风云。然而,目标的不同只会凸显快速结束单芯片设计时代面临的广泛挑战。

图源:top10.digital

图源:top10.digital芯片巨头纷纷入场

多芯片设计不是什么新概念,但直到最近五年才越来越受青睐。AMD、苹果、英特尔和英伟达等芯片巨头都不同程度地涉足其中。

AMD 通过自身的 EPYC 和 RYZEN 处理器在小芯片(chiplet)设计领域展开探索。英特尔在 2021 年架构日活动上发布了下一代英特尔至强可扩展处理器 Sapphire Rapids,这款面向服务器市场的架构使用小芯片「tiles」构建而成。

现在,苹果和英伟达也加入了多芯片设计的行列,尽管面向的目标市场截然不同。应该看到,向多芯片设计的转变是由现代芯片制造中的挑战所驱动的。晶体管小型化的速度已经变慢,但前沿设计中晶体管数量的增长仍未见放缓的迹象。

以苹果 M1 Ultra 芯片为例,它的晶体管数量为 1140 亿,是个人计算机芯片中有史以来最多的,为 M1 的 7 倍。单个 M1 Max 的芯片面积为 432 平方毫米,由此推知,M1 Ultra 的面积约为 860 平方毫米(官方数字未知)。

M1 Ultra 示意图。

M1 Ultra 示意图。英伟达 Grace CPU 的晶体管数量处于保密状态,但与它一起发布的 Hopper H100 GPU 拥有 800 亿个晶体管,20 块即可承载全球流量。2019 年,AMD 发布的 64 核 EYPC Rome 处理器拥有 395 亿个晶体管。

英伟达 Grace CPU 超级芯片。

英伟达 Grace CPU 超级芯片。市场研究公司 Counterpoint Research 的研究分析师 Akshara Bassi 表示,「随着芯片面积变得越来越大以及晶圆成品率问题越来越重要,多芯片模块封装设计能够实现比单芯片设计更佳的功耗和性能表现。」

目前,除了致力于造出单个完整硅晶圆的 AI 芯片创业公司 Cerebras 之外,芯片行业似乎达成了一致意见,即单芯片设计变得越来越「得不偿失」。

2021 年 4 月,Cerebras 发布了 2.6 万亿晶体管、比 ipad 还大的巨无霸芯片 WSE 2。

此外,行业转向小芯片与芯片制造商的支持是同步进行的。2020 年 8 月,全球最大芯片代工厂台积电推出了 3DFabric 先进封装技术系列,包含了前端 3D 硅堆栈和后端封装技术。

AMD 在其 EPYC 和 RYZEN 处理器设计中使用了属于 3DFabric 的技术,并且几乎可以肯定苹果 M1 Ultra 芯片也使用了台积电相关封装技术(虽然苹果尚未给予确认,但 M1 Ultra 是由台积电制造的)。

其他芯片巨头如英特尔,它有自己的封装技术,如 EMIB 和 Foveros。尽管最开始意在自己使用,但随着英特尔代工服务的开展,该公司的芯片制造技术正变得与更广泛的行业息息相关。

多芯片设计的前景如何?

另一家市场研究公司 Hyperion Research 的一位高级分析师 Mark Nossokoff 认为,「围绕基础半导体设计、制造和封装的生态已经发展到了能够支持『设计节点经济可靠生成小芯片解决方案』的程度。无缝集成多样化小芯片功能的软件设计工具也已经成熟到可以优化目标解决方案的性能了。」

小芯片将继续存在,但就目前而言,该领域是一个孤岛。AMD、苹果、英特尔和英伟达正在将自研的互连设计方案应用于特定的封装技术中。

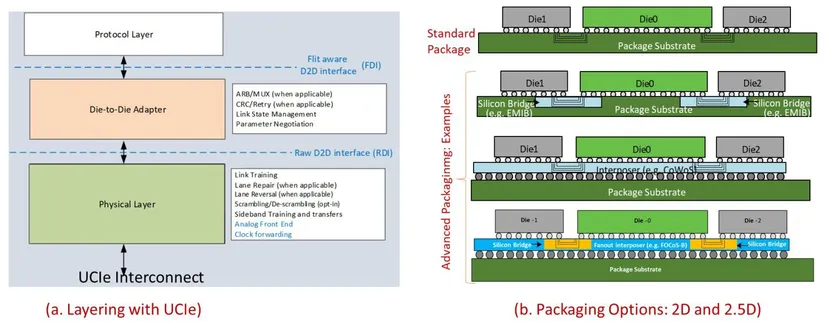

今年 3 月 2 日,英特尔、AMD、Arm、高通、台积电、三星、日月光、谷歌云、Meta、微软等十大巨头宣布成立 Chiplet 标准联盟,推出了通用小芯片互连标准(Universal Chiplet Interconnection Express, UCIe),希望将行业聚合起来。该标准提供了一个面针对成本效益性能的「标准」2D 包和面向前沿设计的「高级」包。

UCIe 还支持通过 PCIe 和 CXL 进行封装之外(off-package)的连接,从而为高性能计算环境中跨多台机器连接多个芯片提供了可能。

UCIe 白皮书中 UCIe 封装方案示例。

UCIe 白皮书中 UCIe 封装方案示例。UCIe 标准是一个开始,它的未来仍有待观察。Nossokoff 对此表示,最初发起 UCIe 的创始成员代表了众多技术设计和制造领域的杰出贡献者,但很多主要组织并没有加入进来,包括苹果、AWS、博通、IBM、英伟达以及其他硅代工厂和内存芯片供应商。

Bassi 指出,英伟达可能特别不愿意加入 UCIe 联盟。英伟达已经为定制硅集成开放了自研的 NVLink-C2C 互连技术,使其成为了 UCIe 的潜在竞争对手。

虽然 UCIe 和 NVLink-C2C 等芯片互连技术的命运决定了行业游戏规则,但它们不太可能改变行业现有局面。

原文链接:https://spectrum.ieee.org/single-chip-processors-have-reached-their-limits