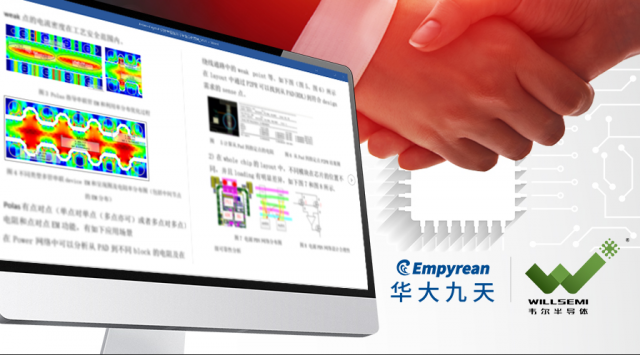

【TechWeb】6月29日消息,国内EDA领军企业北京华大九天科技股份有限公司近日宣布,全球排名前列的中国半导体设计公司,业界知名的电源管理芯片和分立器件提供商豪威集团-上海韦尔半导体股份有限公司 (以下简称“韦尔股份”)已采用华大九天的Empyrean Polas®工具作为其可靠性分析解决方案,更大限度保障分立器件和电源芯片的设计可靠性及设计合理性。

Empyrean Polas®是一款适用于IC版图设计和分立器件版图设计的可靠性和设计合理性分析工具,能够结合PCB和封装设计,形成完整系统分析解决方案。

在电源管理芯片设计中,工程师可运用Empyrean Polas®进行Power MOS导通电阻Rdson(包括Inter-connection、PCB及Package)分析、导通路径的EM/IR-drop分析、MOSFET开启信号延迟以及信号完整性分析等,对芯片核心组件进行全方位性能可靠性检查。此外,将Empyrean Polas®用于芯片PDN网络、关键路径网络电阻以及EM/IR-drop分析,可进一步指导优化设计。

“随着设计复杂度的提升,Power设计场景也趋于复杂。除了单管,不同类型的多管串联也成为设计的一部分,华大九天的Polas工具对于多管串联等复杂设计的Rdson和EM分析中有很好的指导作用,从Rdson的分net分层次的结果展示以及EM分析展示的PAD电流和分net分层次的EM/IR-drop展示,能很好地帮助我们发掘连线问题、PAD分布问题和可靠性问题,并能在保证可靠性前提下减少冗余,指导优化版图,减小芯片面积。”韦尔股份旗下企业,豪威模拟集成电路(北京)有限公司研发总监林建辉对Polas在电源管理芯片设计中的表现予以肯定。

在分立器件设计中,Empyrean Polas®可计算各种工艺场景下分立器件的导通电阻Rdson,分析 conductor layer、PCB和Package设计的可靠性分析和合理性,指导器件和版图设计、测试和封装方案等。

韦尔股份MOS器件设计经理董建新在回顾双方的探索合作时讲到,“在传统分立器件设计流程中,不同工艺参数下的导通电阻、芯片的可靠性、测量针卡的制作都是通过不断流片、制作多版针卡并测试的方式完成,研发周期长、成本高,并且由于wafer的差异性和测试的差异性,往往得不到想要的结论。通过与华大九天合作,我们第一次创新性地在分立器设计中引入可靠性和设计合理性工具,在设计阶段从layout出发,模拟出整个芯片各个工艺参数下的导通电阻、完善可靠性方案以及不同测试针卡下预期测试结果。按此方案,已完成数十颗产品的参数适配,与测试数据的误差多数在3%以内,整体在5%以内。目前此方案已导入到设计的主流程,减少研发阶段流片次数和针卡制作次数,缩短研发周期,降低研发成本。”