记者/彭新

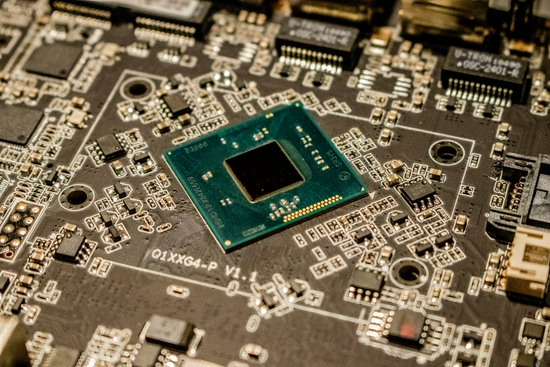

摩尔定律在芯片制造领域会延续下去吗?当以英特尔、台积电和三星为代表的芯片制造厂商将它证明了数十年之后,回答问题的关键已不是“会”与“不会”,而是如何延续下去。

多年以来,在手机、电脑应用的驱动下,台积电、英特尔不断改进芯片的生产工艺,与英特尔联合创始人戈登·摩尔50年前提出的摩尔定律保持一致。然而近年,芯片工艺越来越接近半导体的物理极限,成本也更加高昂,追赶“摩尔定律”愈加困难。

“为什么说摩尔定律到头了,因为经济学上它的成本反而增加了。” EDA((电子设计自动化)软件公司Cadence数字与签核事业部产品工程资深群总监刘淼告诉界面新闻。

粗略计算,以1美元对应制造的晶体管长度计算,2012年的28纳米制程可以制造约20米晶体管,到了2014年的20纳米制程,则仍只有20米。“光靠这一个维度(先进制程)是不足以支撑摩尔定律继续往下走的,因为它的成本看不到显著的降低。”刘淼说。

从设计到制造,越来越多的芯片产业链企业开始尝试新方案。从整个行业来看,行业龙头台积电投入5纳米及3纳米先进制程时,在先进封装技术上也持续推进,小芯片(Chiplet)系统封装正成为台积电主要客户所看重的技术。两者对比而言,由于先进制程成本极为昂贵,后者应用趋势已经变得明显。

AMD首席执行官苏姿丰认为,摩尔定律仍然有效,但推进的速度趋缓。过去半导体业靠先进制程微缩,让芯片体积不变,但晶体管密度倍数提升,如今发展逐渐面临瓶颈,必须靠Chiplet封装、异质整合等技术协助智能微缩下,芯片效能才能提升。

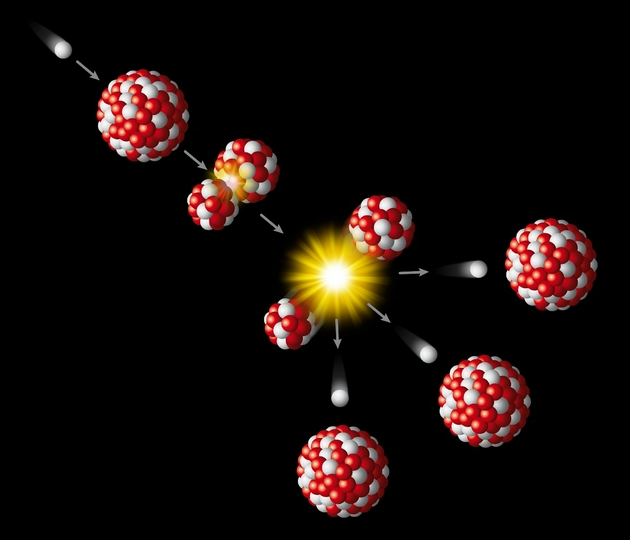

Chiplet近年成为芯片行业的关键词。传统系统单芯片的做法是每一个组件放在单一裸晶(Die)上,造成功能越多,硅芯片尺寸越大。Chiplet的特点是将大尺寸的多核心设计分散到个别微小裸芯片,如处理器、模拟组件、储存器等,再用立体堆栈的方式,以封装技术做成一颗芯片,类似乐高积木。

实际上,产业界早就意识到3D结构对于延续和“拯救”摩尔定律的意义:面对非常小的设备尺寸,物理定律已成为晶体管技术进步的障碍。

在中国,现任中芯国际副董事长蒋尚义近年来即致力于Chiplet封装。此前他在公开场合曾表示,这些年集成电路不断创新,发展至今摩尔定律已经接近其物理极限,未来改变方向在于整个系统中的瓶颈:封装与电路板。

“我自己在2009年时就开始做先进封装,我们希望打破这个瓶颈。” 蒋尚义提及,如有了先进封装,整个系统架构将完全改变。未来半导体方向将不再是芯片越做越小、功能越来越好、功耗越来越低,而是将一个大的芯片分成小的芯片,再重新组合。

Chiplet系统级封装技术被视为减缓摩尔定律失效的对策。在台积电宣布与ARM合作了第一个以CoWaS(基板上晶圆上封装)解决方案获得硅晶验证的7纳米小芯片系统产品后,包括AMD和联发科也是Chiplet的拥趸。

不过,3D堆叠也意味着设计复杂性大大增加。芯片设计本身作为一个极度复杂的问题,平面布局往往需要花费数月来微调和优化,Chiplet的堆积木方式也带来了新维度的挑战和更长的设计周期。在管理上,以往芯片的SoC(系统级芯片)设计和封装团队各自为战,带来合作上的难度。

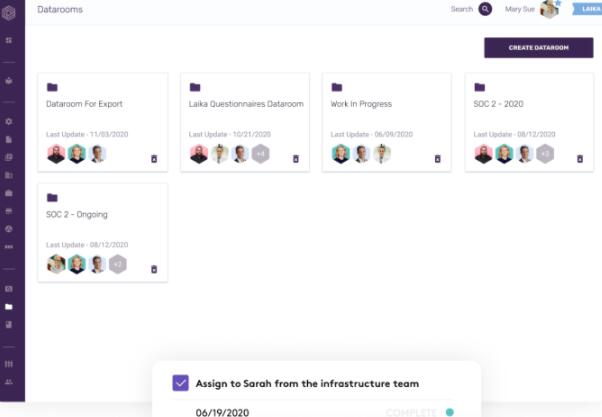

对此, Cadance试图给出方案,他们开发的一种新的芯片设计平台,称为Integrity 3D-IC平台,能在芯片3D设计中开发更强大和更高能效的计算机芯片,同时加快设计时间。透过热完整性、功率和静态时序分析能力,为客户提供以系统级PPA表现,使之在单一小芯片(Chiplets)中能妥善发挥性能。

在芯片产业中处于上游的EDA软件公司转向推动和支持芯片3D堆叠,有助于芯片3D设计在芯片设计和制造领域加快普及。

在芯片制造领域,台积电与AMD合作,使用7纳米技术生产服务器芯片,同时基于Chiplet小芯片系统级封装、新型芯片架构,试图达到摩尔定律所预期的半导体效能提升效果。同时,在芯片设计上,Cadance也与光子AI芯片公司 Lightelligenc合作,将光子芯片和硅芯片进行堆叠,完成高效能的AI芯片设计。

从长期来看,将3D堆叠技术应用于7纳米甚至更高制程,提高各工艺节点设计的性能,并降低功耗,其技术普及令人期待。

不过,3D堆叠或Chiplet技术的普及,仍有很多课题需要进一步研究,如各微小芯片之间的沟通接口传输效率及功耗等。但如果成功实现,延续摩尔定律成为可能,甚至一定程度上会成为中国芯片公司走向世界前列的契机。