作为全球半导体技术的领导者,三星电子刚刚宣布,其已开始用 3nm 工艺节点来制造 GAA 环栅晶体管芯片。可知与 5nm 工艺相比,优化后的 3nm 工艺可在收缩 16% 面积的同时,降低 45% 的功耗并提升 23% 的性能。

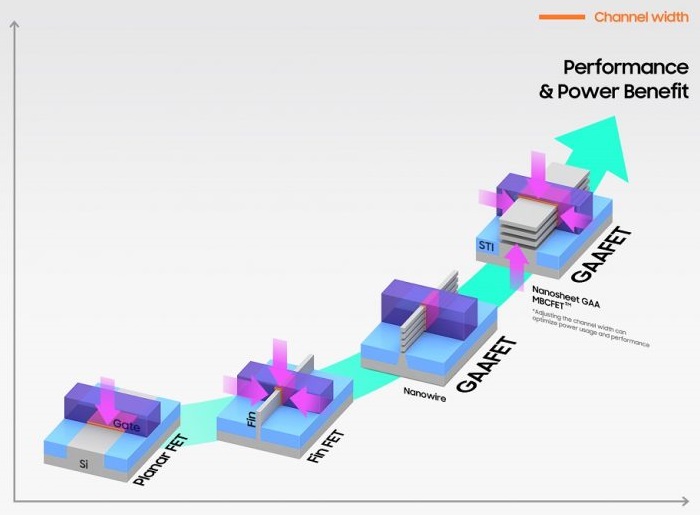

据悉,为突破鳍式场效应晶体管(FinFET)的性能限制,三星选择了多桥通道 FET(简称 MBCEFT)技术来制造首批 GAA 晶体管芯片。通过下调电压水平来提升能源效率,同时增加驱动电流以提升性能。

目前三星正在努力推动 3nm GAA 晶体管和相关半导体芯片在高性能、低功耗计算领域的采用,并且计划将相关优势推广到移动处理器。

左起为公司副总裁 Michael Jeong,执行副总裁 Ja-Jum Ku 和代工业务副总裁 Sang Bom Kang

三星电子总裁兼代工业务负责人 Siyoung Choi 博士称:

三星代工事业部 / 半导体研发中心高管合影庆祝

三星代工事业部 / 半导体研发中心高管合影庆祝与使用更窄通道的纳米线 GAA 方案相比,三星专有技术选择了更宽的通道。该公司有能力调节 3nm GAA 纳米片的通道宽度,结合优化的功耗与性能表现,以满足客户的各种需求。

此外 GAA 的设计灵活性,对于设计技术的协同优化(DTCP)也非常有利 —— 有助于增强功耗、性能和面积(PPA)等方面的优势。

与 5nm 公司相比,三星电子初代 3nm GAA 工艺可较 5nm 降低多达 45% 的功耗,同时提升 23% 的性能和减少 16% 的面积占用。

展望未来,三星第二代 3nm 工艺更是可以将功耗降低多达 50%,同时提升 30% 的性能和减少 35% 的面积占用。

最后,随着制程节点不断缩小、以及各行业客户对于芯片性能需求的日渐提升,IC 设计人员也面临着处理大量数据、以验证具有更多功能和紧密扩展的复杂产品的挑战。

为满足这些需求,三星也在努力提供更稳定的设计环境,以帮助减少设计、验证和签核过程所需的时间,同时提升产品的可靠性。

自 2021 年 3 季度以来,三星电子携手包括 Ansys、Cadence、Siemens 和 Synopsys 在内的先进代工生态系统(简称 SAFE)合作伙伴做了广泛而充分的准备,以带来经过验证的设计基础设施,进而帮助客户在更短的时间内完善其产品。