今天,分享一篇联华电子和 Cadence 共同合作开发 3D-IC 混合键合(hybrid-bonding)参考流程,希望以下联华电子和 Cadence 共同合作开发 3D-IC 混合键合(hybrid-bonding)参考流程的内容对您有用。

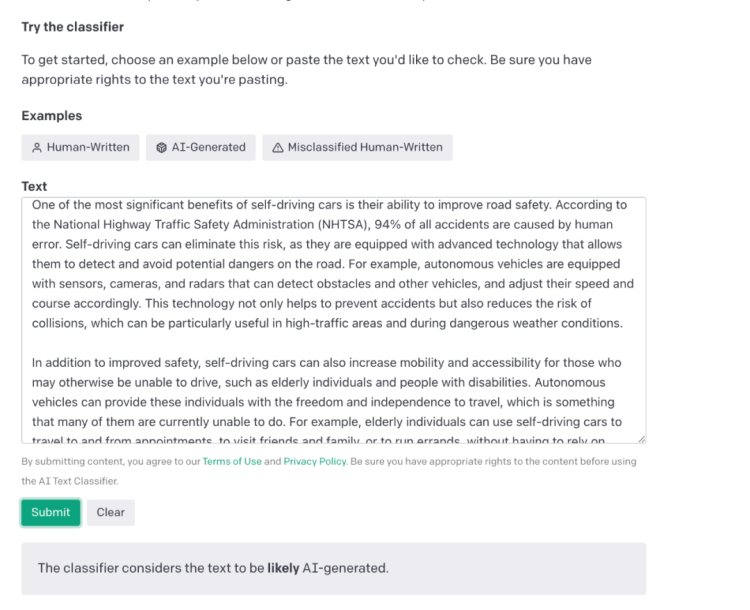

【TechWeb】2月1日消息,联华电子与楷登电子(美国 Cadence)今日共同宣布,采用 Integrity™ 3D-IC 平台的 Cadence® 3D-IC 参考工作流程已通过联电的芯片堆栈技术认证,将进一步缩短产品上市时间。

联电的混合键合解决方案已经做好支持广泛技术节点集成的准备,适用于边缘 AI、图像处理和无线通信应用。采用联电的 40nm 低功耗(40LP)工艺作为片上堆栈技术的展示,双方合作验证了该设计流程中的关键 3D-IC 功能,包括使用 Cadence 的 Integrity 3D-IC 平台实现系统规划和智能桥突创建。Cadence Integrity 3D-IC 平台是业界首款综合解决方案,在单一平台中集成了系统规划、芯片和封装实现以及系统分析。

该参考流程以 Cadence 的 Integrity 3D-IC 平台为核心,围绕高容量、多技术分层的数据库构建而成。该平台在统一的管理平台下提供 3D 设计完整的设计规划、实现和分析。通过在设计初期执行热能、功耗和静态时序分析,可以实现 3D 芯片堆栈中的多个晶粒的同步设计和分析。该流程还支持针对连接精度的系统级布局与原理图(LVS)检查,针对覆盖和对齐的电气规则检查(ERC),以及在 3D 堆栈设计结构中的热分布分析。

除了 Integrity 3D-IC 平台,Cadence 3D-IC 流程还包括 Innovus™ 设计实现系统,Quantus™ 寄生提取解决方案,Tempus™ 时序签核解决方案,Pegasus™ 验证系统,Voltus™ IC 电源完整性解决方案和Celsius™ 热求解器。